*Professional*<sup>TM</sup>

300 Series

---

Technical Manual

Volume 2 Options

First Edition, July 1985

Copyright © 1985 by Digital Equipment Corporation.

All Rights Reserved.

Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited.

For copy information, contact the Educational Services Department,

Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors

that may appear in this document.

This equipment has been certified to comply with the limits for a Class B

computing device, pursuant to Subpart J of Part 15 of FCC Rules. Only

peripherals (computer input/output devices, terminals, printers, etc.)

certified to comply with the Class B limits may be attached to this

computer. Operation with noncertified peripherals is likely to result in

interference to radio or television reception.

Z80 is a trademark of Zilog Corporation

CP/M is a trademark of Digital Research, Inc.

Airlock is a trademark of Quantum Corporation

Mate-N-Lok is a trademark of AMP, Inc.

The following are trademarks of Digital Equipment Corporation,

Maynard, Massachusetts.

|              |           |              |                |

|--------------|-----------|--------------|----------------|

| digital™     | DECUS     | P/OS         | TMS            |

| CTI BUS      | DECwriter | Professional | UNIBUS         |

| DEC          | DIBOL     | Rainbow      | VAX            |

| DECmate      | Digital   | RSTS         | VMS            |

| DECnet       | IVIS      | RSX          | VT             |

| DECsystem-10 | MASSBUS   | RT           | Work Processor |

| DECSYSTEM-20 | PDP       |              |                |

# CONTENTS

## INTRODUCTION

### CHAPTER 1 TELEPHONE MANAGEMENT SYSTEM

|         |                                               |      |

|---------|-----------------------------------------------|------|

| 1.1     | Introduction .....                            | 1-1  |

| 1.1.1   | Related Documentation .....                   | 1-1  |

| 1.1.2   | Physical Description .....                    | 1-2  |

| 1.1.2.1 | TMS Controller Module .....                   | 1-2  |

| 1.1.2.2 | Telephone Line Interface (TLI) Module .....   | 1-3  |

| 1.1.2.3 | Voice Unit .....                              | 1-3  |

| 1.2     | TMS System Level Functional Description ..... | 1-4  |

| 1.2.1   | TMS Controller Module .....                   | 1-4  |

| 1.2.1.1 | Microprocessor Subsystem .....                | 1-6  |

| 1.2.1.2 | CTI Bus Interface .....                       | 1-6  |

| 1.2.1.3 | Memory Subsystem .....                        | 1-6  |

| 1.2.1.4 | I/O Processing Subsystem .....                | 1-6  |

| 1.2.1.5 | Communications Subsystem .....                | 1-7  |

| 1.2.1.6 | Crossbar Switching Circuit .....              | 1-7  |

| 1.2.1.7 | TLI/Voice Unit Interface .....                | 1-7  |

| 1.2.1.8 | Call Progress Tone Detector .....             | 1-7  |

| 1.2.2   | Telephone Line Interface (TLI) Module .....   | 1-8  |

| 1.2.2.1 | Line Switching Relay Circuits .....           | 1-8  |

| 1.2.2.2 | Line Coupling Circuit .....                   | 1-8  |

| 1.2.2.3 | Ring-In Detector Circuit .....                | 1-8  |

| 1.2.2.4 | Off-Hook Detector Circuit .....               | 1-8  |

| 1.2.2.5 | Voice Unit Interface .....                    | 1-8  |

| 1.2.3   | Voice Unit .....                              | 1-8  |

| 1.2.3.1 | 8051 Microcomputer .....                      | 1-9  |

| 1.2.3.2 | Keyboard .....                                | 1-9  |

| 1.2.3.3 | LED Display .....                             | 1-9  |

| 1.2.3.4 | Speaker .....                                 | 1-9  |

| 1.2.3.5 | Microphone .....                              | 1-10 |

| 1.2.3.6 | Remote Equipment Jack .....                   | 1-10 |

| 1.3     | Detailed Description .....                    | 1-10 |

| 1.3.1   | TMS Controller Module .....                   | 1-10 |

| 1.3.1.1 | 8031 Microprocessor Subsystem .....           | 1-10 |

| 1.3.1.2 | CTI Bus Interface Circuit Subsystem .....     | 1-14 |

|         |                                             |      |

|---------|---------------------------------------------|------|

| 1.3.1.3 | Memory Subsystem .....                      | 1-17 |

| 1.3.1.4 | I/O Processing Subsystem .....              | 1-19 |

| 1.3.1.5 | Communications Subsystem .....              | 1-21 |

| 1.3.1.6 | Crossbar Switching Circuit .....            | 1-31 |

| 1.3.1.7 | Call Progress Tone Detector .....           | 1-32 |

| 1.3.1.8 | TLI/Voice Unit Interface Circuit .....      | 1-32 |

| 1.3.2   | Telephone Line Interface (TLI) Module ..... | 1-34 |

| 1.3.2.1 | Relay Circuits .....                        | 1-35 |

| 1.3.2.2 | Line Coupler Circuits .....                 | 1-35 |

| 1.3.2.3 | Ring-In Detector Circuit .....              | 1-36 |

| 1.3.2.4 | Telset Off-Hook Detector Circuit .....      | 1-36 |

| 1.3.2.5 | Voice Unit Interface .....                  | 1-36 |

| 1.3.3   | Voice Unit .....                            | 1-36 |

| 1.3.3.1 | System Overview .....                       | 1-37 |

| 1.3.3.2 | Detailed Description .....                  | 1-39 |

| 1.4     | Connector Descriptions .....                | 1-40 |

| 1.5     | Hardware Specifications .....               | 1-43 |

## CHAPTER 2 CP/M OPTION MODULE

|         |                                          |      |

|---------|------------------------------------------|------|

| 2.1     | Introduction .....                       | 2-1  |

| 2.1.1   | Related Documentation .....              | 2-2  |

| 2.1.2   | Physical Description .....               | 2-2  |

| 2.2     | Functional Description .....             | 2-3  |

| 2.2.1   | Components .....                         | 2-3  |

| 2.2.1.1 | CTI Bus Interface Circuits .....         | 2-4  |

| 2.2.1.2 | Z80 Microprocessor Circuits .....        | 2-4  |

| 2.2.1.3 | Status Register Circuits .....           | 2-4  |

| 2.2.1.4 | Processor Firmware Logic Circuits .....  | 2-5  |

| 2.2.1.5 | RAM Logic Circuits .....                 | 2-5  |

| 2.3     | Theory of Operation .....                | 2-5  |

| 2.3.1   | CTI Bus Interface Circuits .....         | 2-5  |

| 2.3.1.1 | CTI Bus Access Interface .....           | 2-6  |

| 2.3.1.2 | ROM Data and Address Register .....      | 2-7  |

| 2.3.1.3 | Hardware Command Register .....          | 2-7  |

| 2.3.1.4 | CP/M Option Module Status Register ..... | 2-7  |

| 2.3.1.5 | Inbound Command and Data Register .....  | 2-7  |

| 2.3.1.6 | Outbound Command and Data Register ..... | 2-7  |

| 2.3.2   | Z80 Microprocessor Circuits .....        | 2-8  |

| 2.3.2.1 | Processor Clock .....                    | 2-8  |

| 2.3.2.2 | I/O Multiplexer .....                    | 2-8  |

| 2.3.2.3 | Z80 Microprocessor .....                 | 2-8  |

| 2.3.3   | Z80 Status Register .....                | 2-9  |

| 2.3.3.1 | Z80 Service Flag Buffer .....            | 2-10 |

| 2.3.3.2 | Host Processor Service Flag Buffer ..... | 2-10 |

| 2.3.3.3 | Command and Data Flag Buffer .....       | 2-11 |

| 2.3.3.4 | Status Port .....                        | 2-11 |

| 2.3.4   | Processor Firmware Logic Circuits .....  | 2-11 |

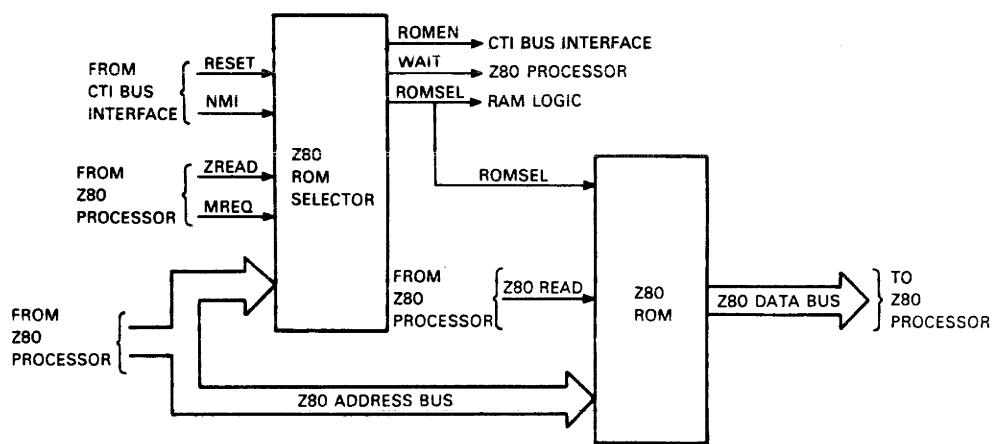

| 2.3.4.1 | Z80 ROM Selector .....                   | 2-11 |

| 2.3.4.2 | Z80 ROM .....                            | 2-12 |

|         |                                                  |      |

|---------|--------------------------------------------------|------|

| 2.3.5   | RAM Logic Circuits .....                         | 2-12 |

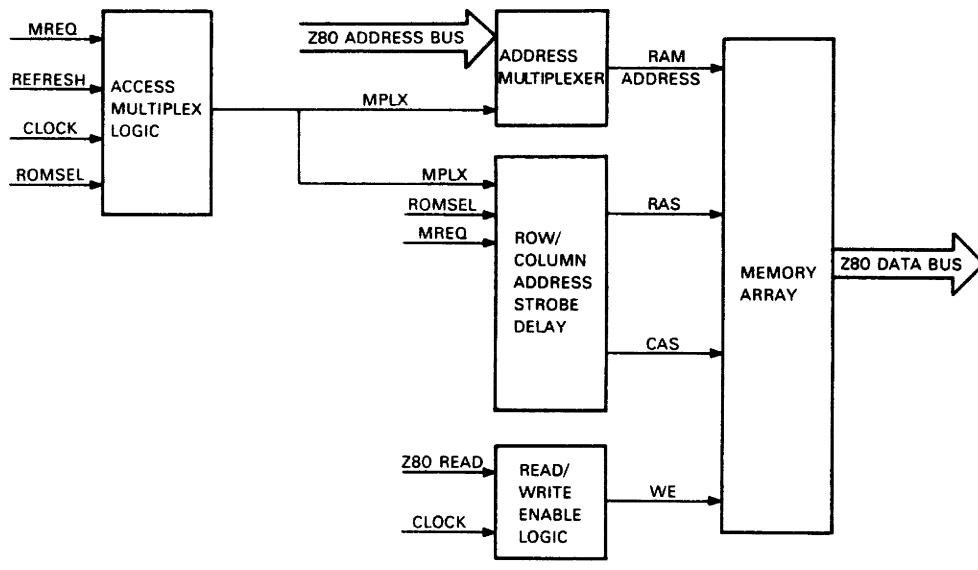

| 2.3.5.1 | Access Multiplex Logic .....                     | 2-13 |

| 2.3.5.2 | Address Multiplexer .....                        | 2-13 |

| 2.3.5.3 | Row/Column Address Strobe Delay .....            | 2-13 |

| 2.3.5.4 | Read/Write Enable Logic .....                    | 2-13 |

| 2.3.5.5 | Memory Array .....                               | 2-13 |

| 2.4     | Connector J1 Description .....                   | 2-13 |

| 2.5     | Programming Registers .....                      | 2-15 |

| 2.5.1   | ROM Data Register (Base+0) .....                 | 2-16 |

| 2.5.2   | Status/Base +0 Reset Register (Base+2) .....     | 2-16 |

| 2.5.2.1 | Nonmaskable Interrupt (NMI) Command Flag .....   | 2-16 |

| 2.5.2.2 | RESET Flag .....                                 | 2-16 |

| 2.5.2.3 | ROM Enable (ROMEN) Flag .....                    | 2-16 |

| 2.5.2.4 | Z80 Halt (ZHALT) Flag .....                      | 2-16 |

| 2.5.2.5 | Interrupt B (IRQB) Flag .....                    | 2-17 |

| 2.5.2.6 | Interrupt A (IRQA) Flag .....                    | 2-17 |

| 2.5.3   | Inbound/Outbound Command Register (Base+4) ..... | 2-17 |

| 2.5.3.1 | Commands to the Host Processor .....             | 2-17 |

| 2.5.3.2 | Software Commands From the Host Processor .....  | 2-17 |

| 2.5.3.3 | Hardware Commands From the Host Processor .....  | 2-17 |

| 2.5.4   | Inbound/Outbound Data Register (Base+6) .....    | 2-17 |

| 2.6     | Operation .....                                  | 2-18 |

| 2.6.1   | Power-Up .....                                   | 2-18 |

| 2.6.1.1 | Z80 Self-Test .....                              | 2-18 |

| 2.6.1.2 | Interface Self-Test .....                        | 2-20 |

| 2.6.2   | Reset and NMI Hardware Commands .....            | 2-20 |

| 2.6.2.1 | RESET Command .....                              | 2-20 |

| 2.6.2.2 | Nonmaskable Interrupt (NMI) Command .....        | 2-20 |

| 2.6.3   | Host Processor Initiated Transfers .....         | 2-20 |

| 2.6.4   | Z80 Microprocessor Initiated Transfers .....     | 2-21 |

| 2.6.5   | Z80 Microprocessor Halt Recovery .....           | 2-21 |

| 2.6.6   | Z80 ROM and RAM Accesses .....                   | 2-21 |

| 2.7     | Specifications .....                             | 2-21 |

## CHAPTER 3 DECNA CONTROLLER OPTION MODULE

|         |                                                                     |     |

|---------|---------------------------------------------------------------------|-----|

| 3.1     | Introduction .....                                                  | 3-1 |

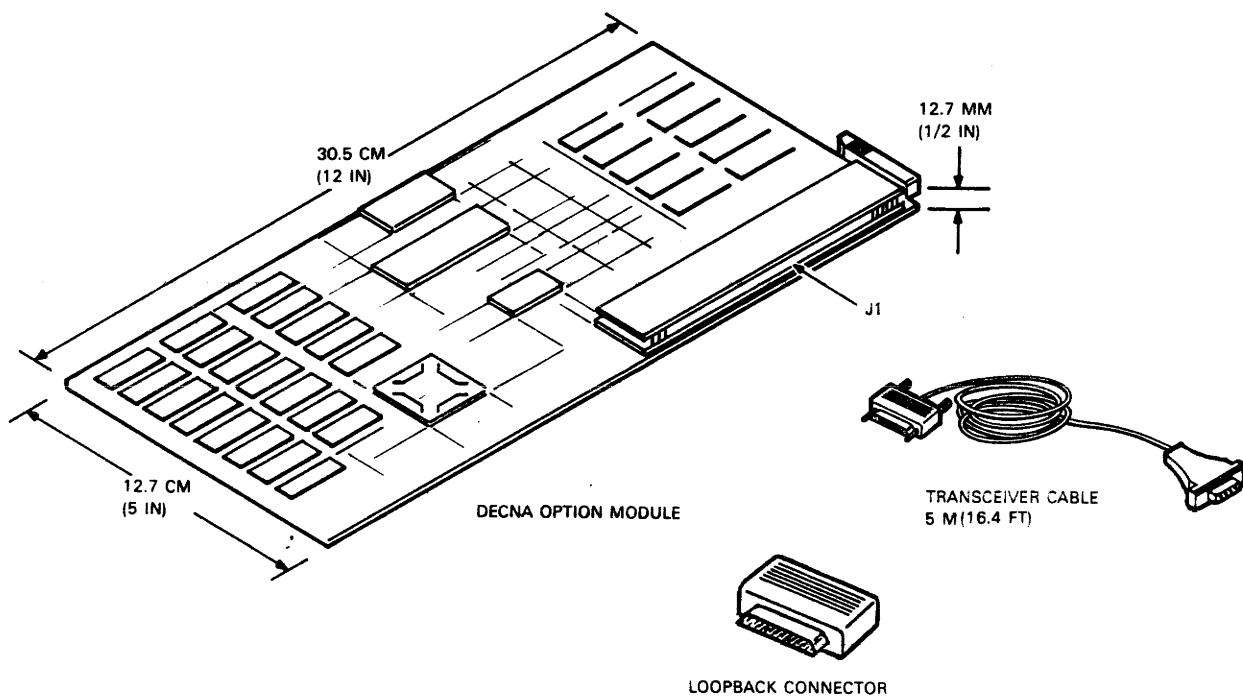

| 3.2     | Physical Description .....                                          | 3-1 |

| 3.3     | Specifications .....                                                | 3-2 |

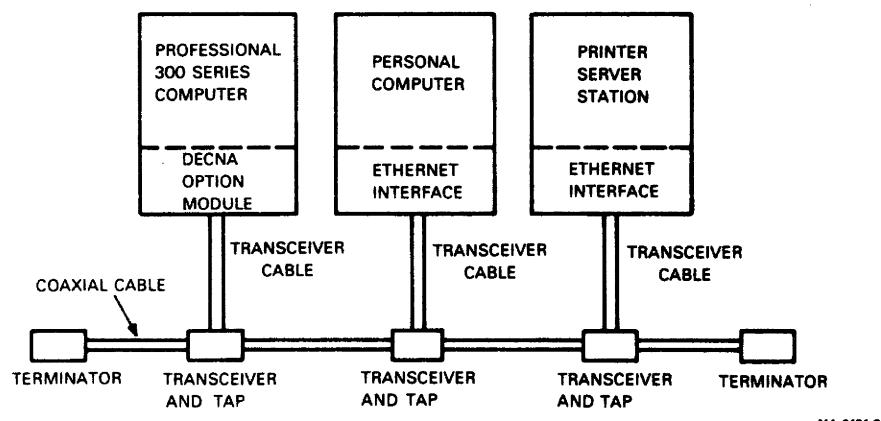

| 3.4     | Ethernet Overview .....                                             | 3-2 |

| 3.4.1   | Main Physical Components .....                                      | 3-2 |

| 3.4.2   | Ethernet Protocol .....                                             | 3-3 |

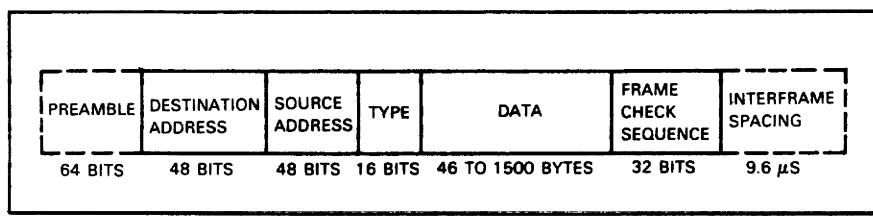

| 3.4.3   | Transmission Frame Format .....                                     | 3-3 |

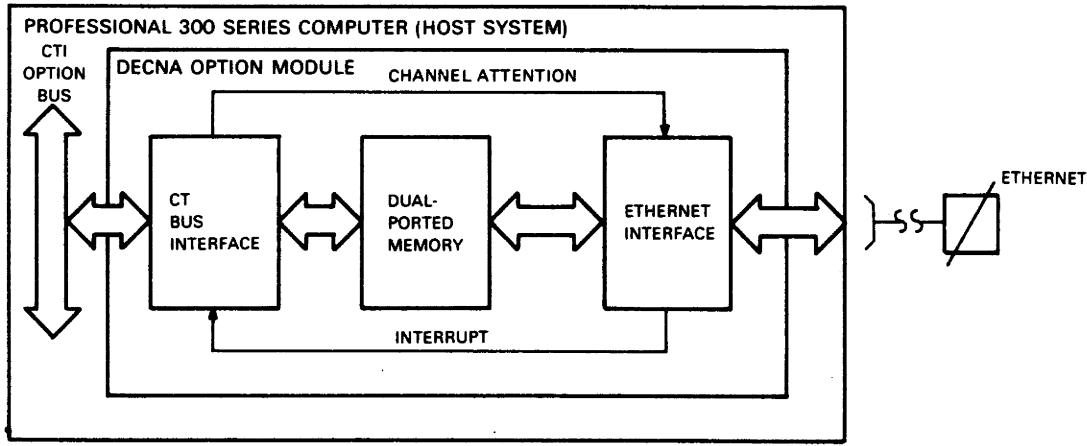

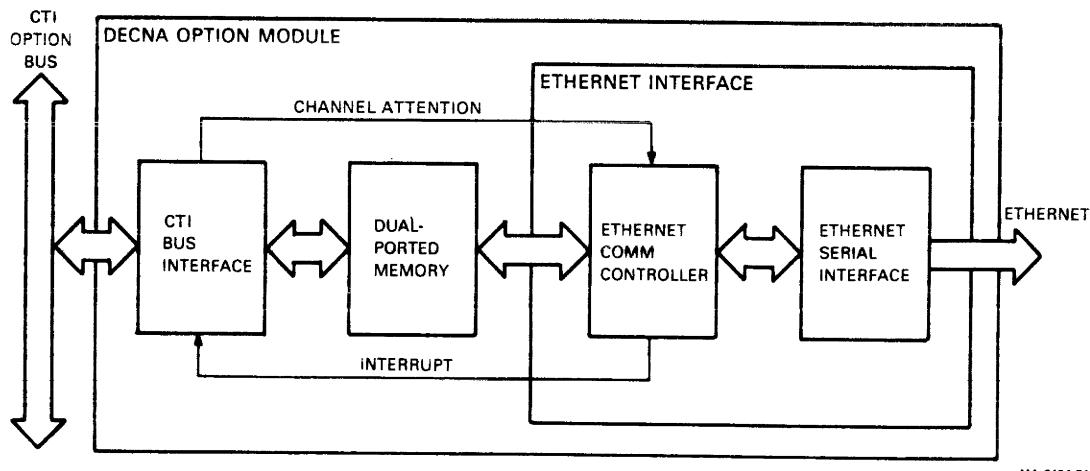

| 3.5     | DECNA Functional Overview .....                                     | 3-4 |

| 3.5.1   | Initialization .....                                                | 3-5 |

| 3.5.2   | Transmission Overview .....                                         | 3-5 |

| 3.5.3   | Reception Overview .....                                            | 3-6 |

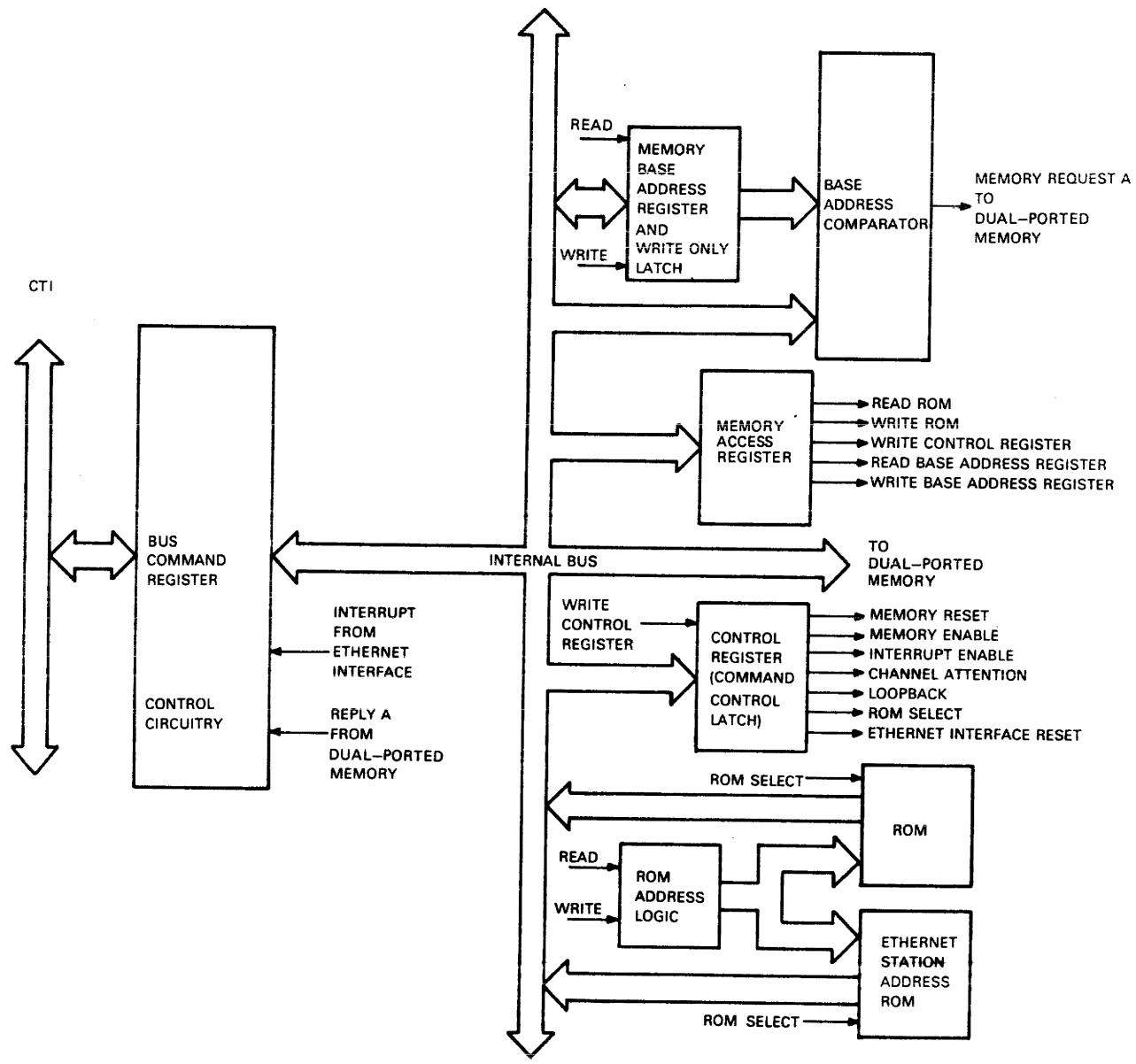

| 3.6     | CTI Bus Interface .....                                             | 3-6 |

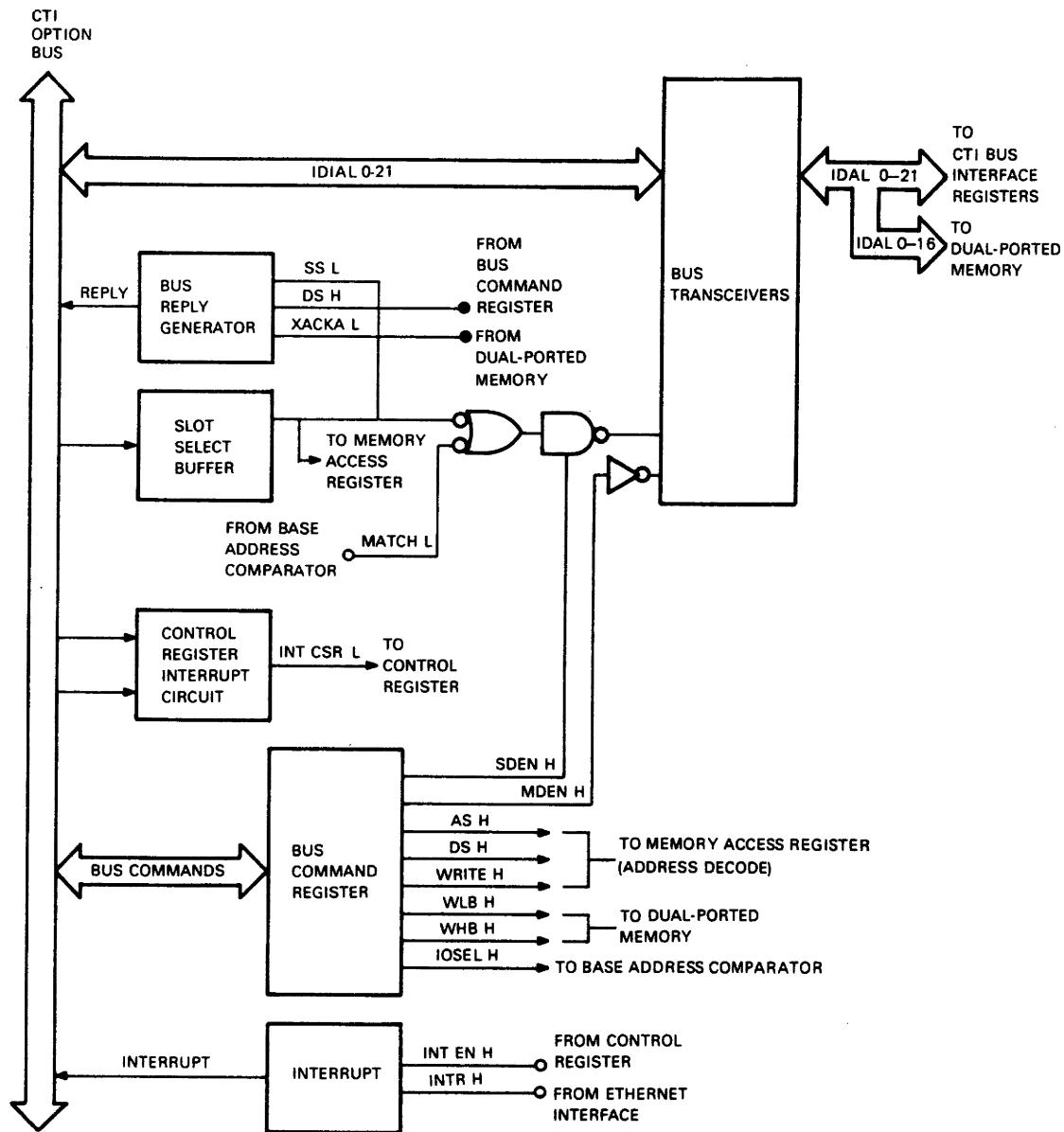

| 3.6.1   | Bus Transceivers, Bus Command Register, and Control Circuitry ..... | 3-6 |

| 3.6.1.1 | Read/Write .....                                                    | 3-6 |

|         |                                                                                                 |      |

|---------|-------------------------------------------------------------------------------------------------|------|

| 3.6.1.2 | Bus Transceivers .....                                                                          | 3-11 |

| 3.6.1.3 | Bus Command Register .....                                                                      | 3-11 |

| 3.6.1.4 | Slot Select Buffer .....                                                                        | 3-11 |

| 3.6.1.5 | Bus Reply Generator .....                                                                       | 3-11 |

| 3.6.1.6 | Control Register Interrupt Circuit .....                                                        | 3-11 |

| 3.6.1.7 | Host Interrupt Circuit .....                                                                    | 3-11 |

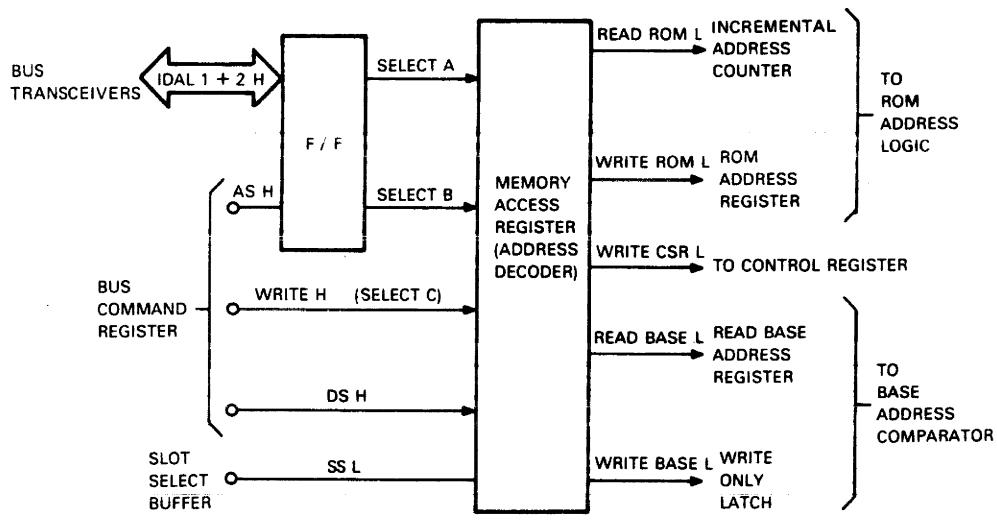

| 3.6.2   | Memory Access Register .....                                                                    | 3-11 |

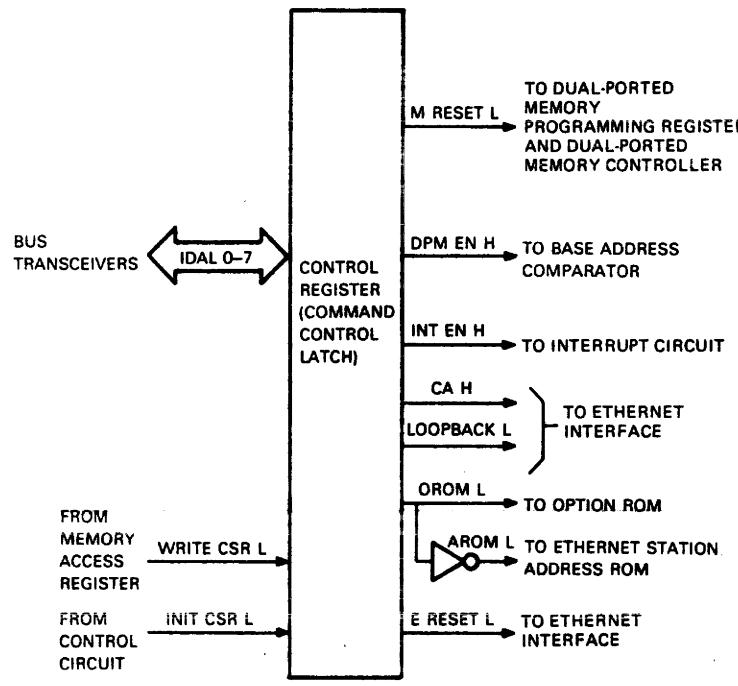

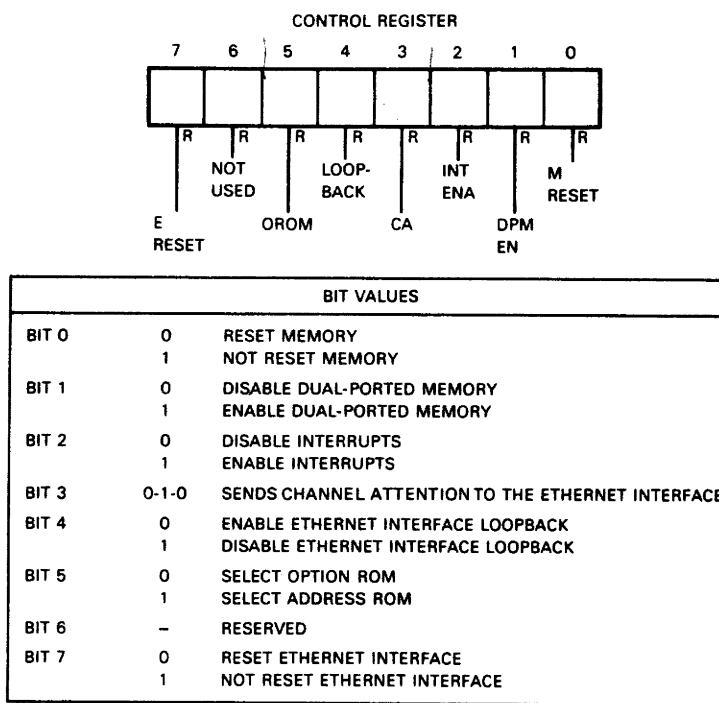

| 3.6.3   | Control Register (Command Control Latch) .....                                                  | 3-13 |

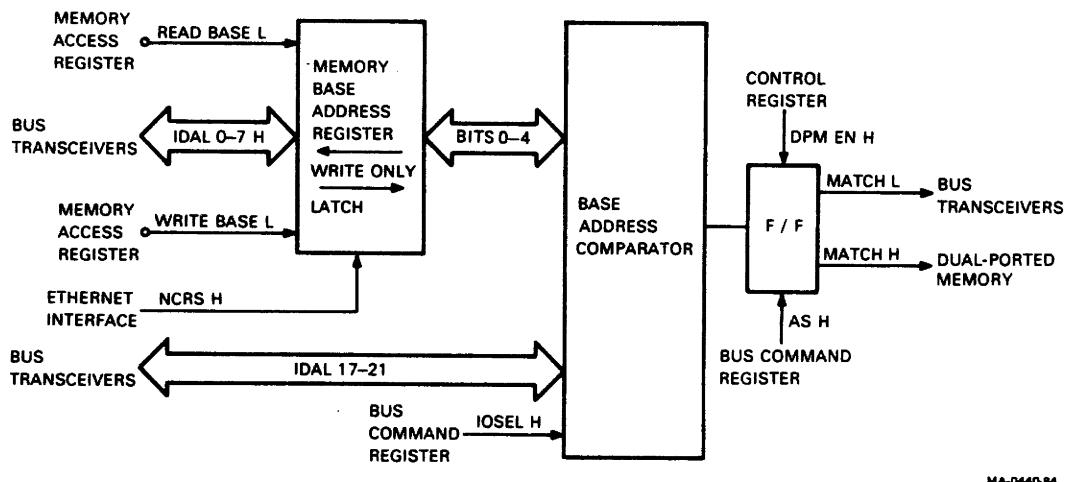

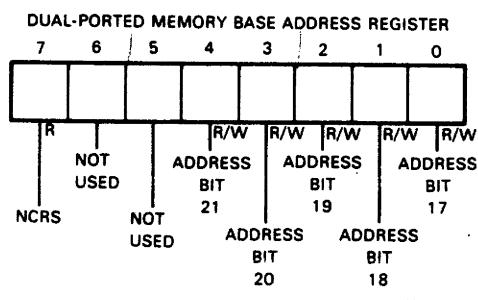

| 3.6.4   | Memory Base Address Register and Write-Only Latch, and<br>Base Address Comparator .....         | 3-16 |

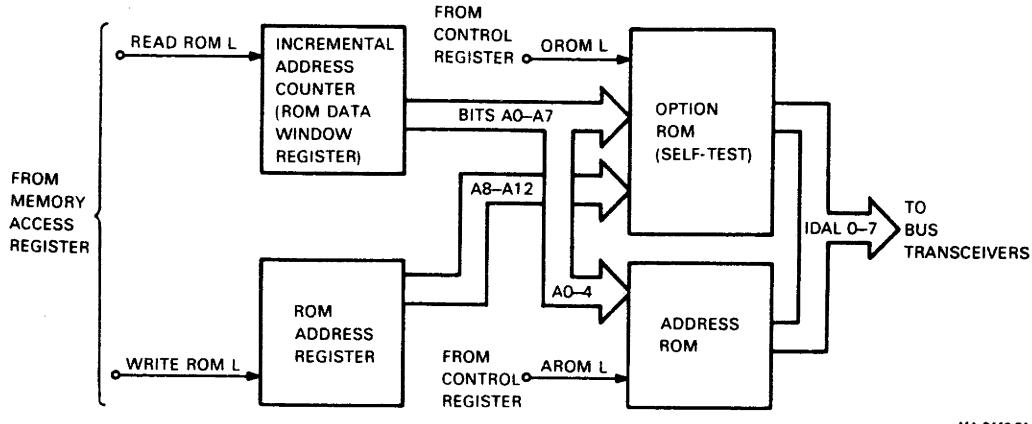

| 3.6.5   | Option ROM, Address ROM, and ROM Address Logic .....                                            | 3-18 |

| 3.6.5.1 | Option ROM .....                                                                                | 3-18 |

| 3.6.5.2 | Address ROM .....                                                                               | 3-18 |

| 3.6.5.3 | ROM Address Logic .....                                                                         | 3-18 |

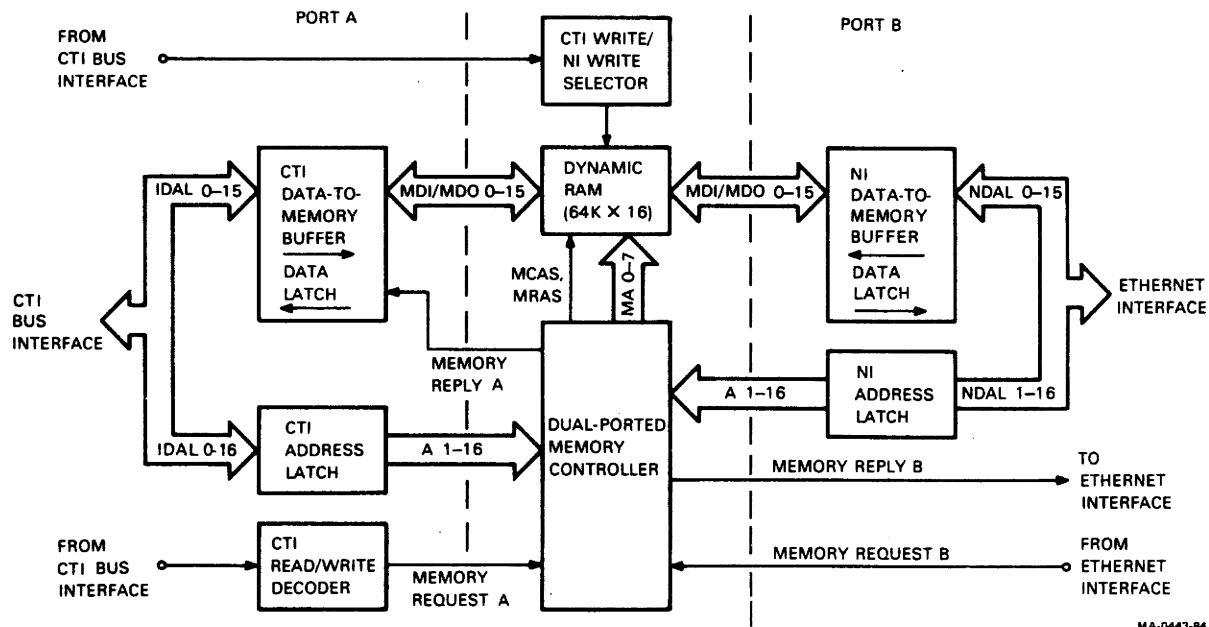

| 3.7     | Dual-Ported Memory .....                                                                        | 3-20 |

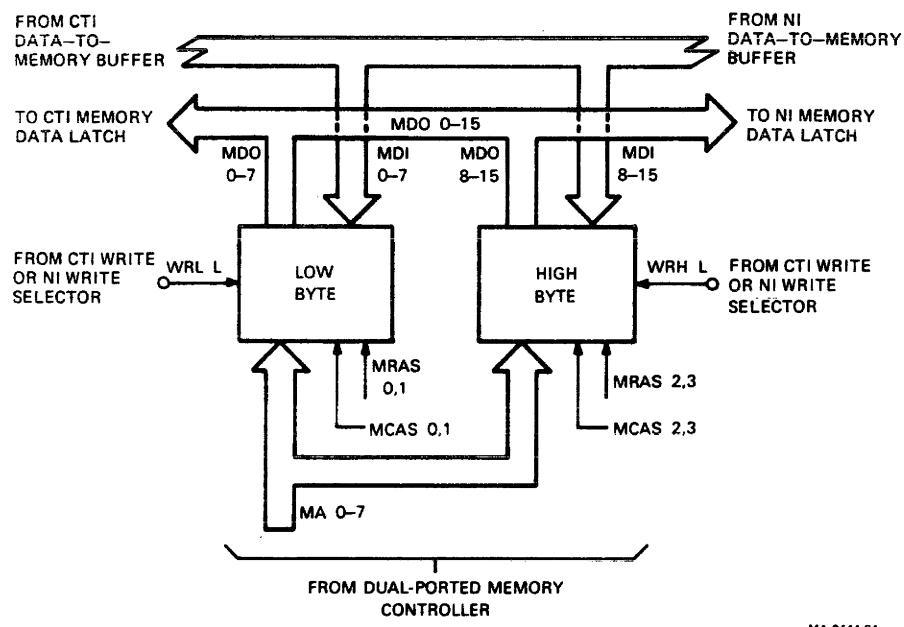

| 3.7.1   | Dynamic RAM .....                                                                               | 3-21 |

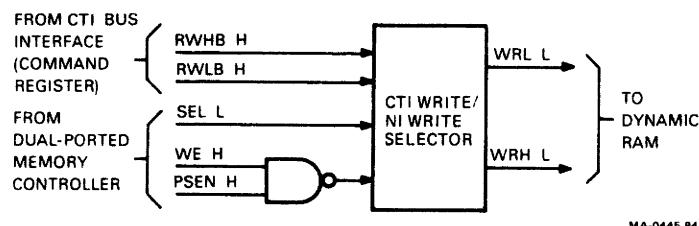

| 3.7.2   | CTI Write/NI Write Selector .....                                                               | 3-22 |

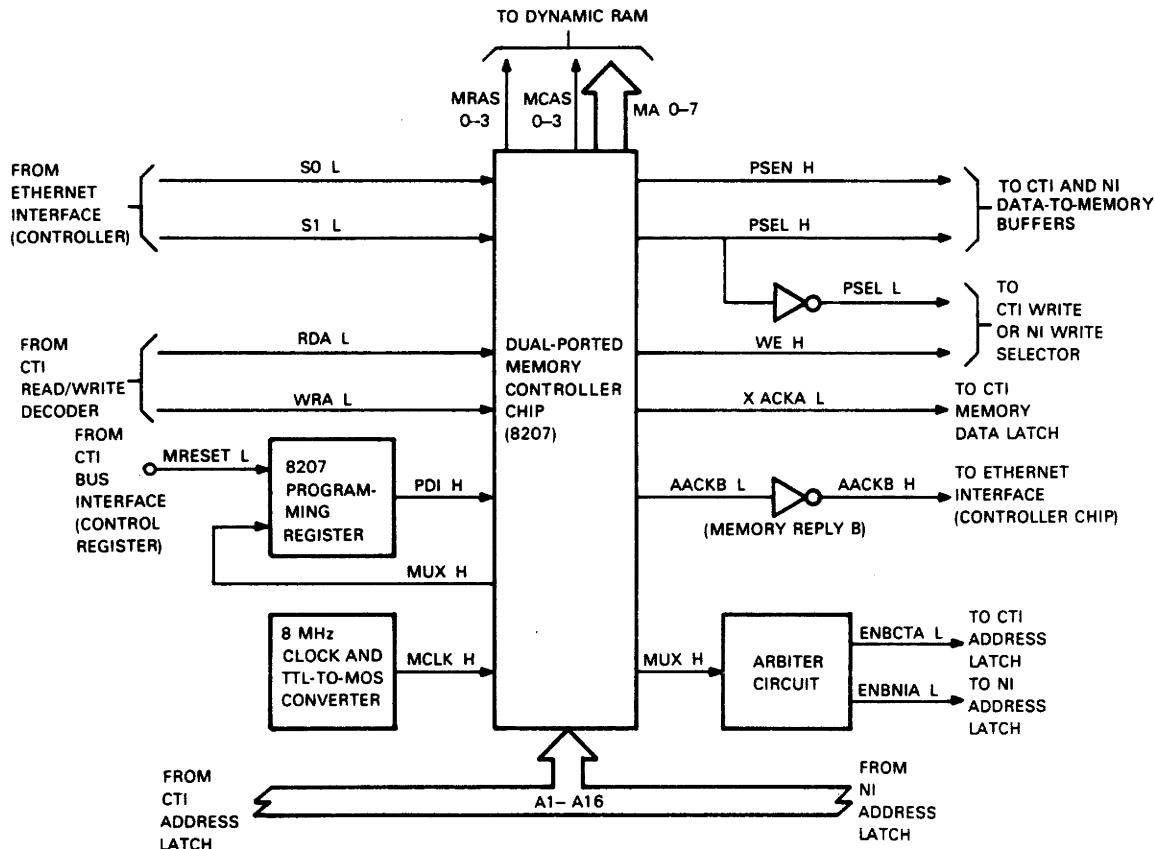

| 3.7.3   | Dual-Ported Memory Controller .....                                                             | 3-24 |

| 3.7.3.1 | Clock and TTL-to-MOS Level Converter .....                                                      | 3-24 |

| 3.7.3.2 | 8207 Programming Register .....                                                                 | 3-24 |

| 3.7.3.3 | Arbiter Circuit .....                                                                           | 3-24 |

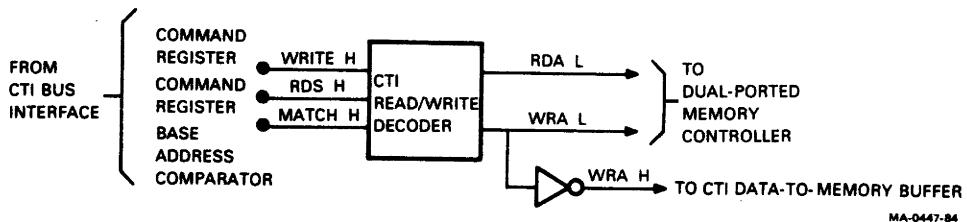

| 3.7.4   | CTI Read/Write Decoder .....                                                                    | 3-27 |

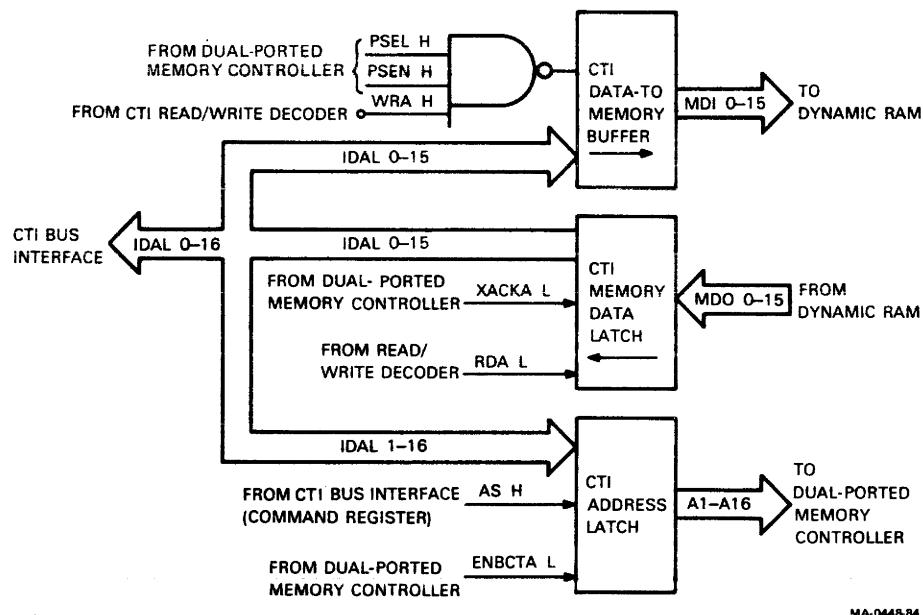

| 3.7.5   | Port A (CTI Data-to-Memory Buffer, Data Latch, and Address Latch) .....                         | 3-29 |

| 3.7.5.1 | CTI Data-to-Memory Buffer .....                                                                 | 3-29 |

| 3.7.5.2 | CTI Memory Data Latch .....                                                                     | 3-29 |

| 3.7.5.3 | CTI Address Latch .....                                                                         | 3-29 |

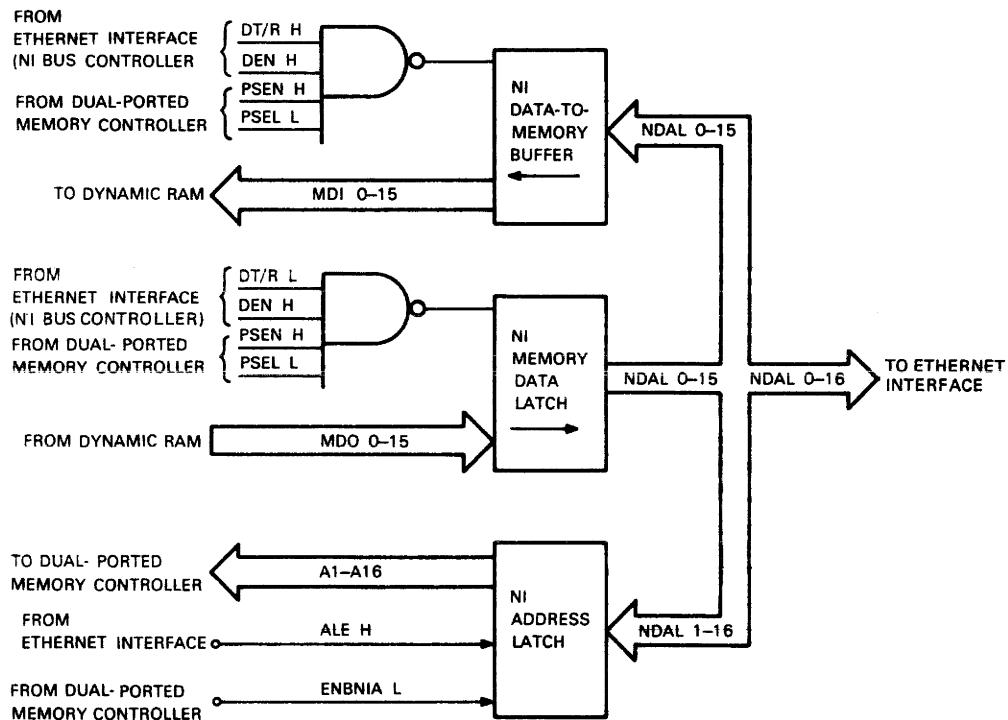

| 3.7.6   | Port B (Network Interface Data-to-Memory Buffer, Memory Data<br>Latch, and Address Latch) ..... | 3-31 |

| 3.7.6.1 | NI Data-to-Memory Buffer .....                                                                  | 3-33 |

| 3.7.6.2 | NI Memory Data Latch .....                                                                      | 3-33 |

| 3.7.6.3 | NI Address Latch .....                                                                          | 3-33 |

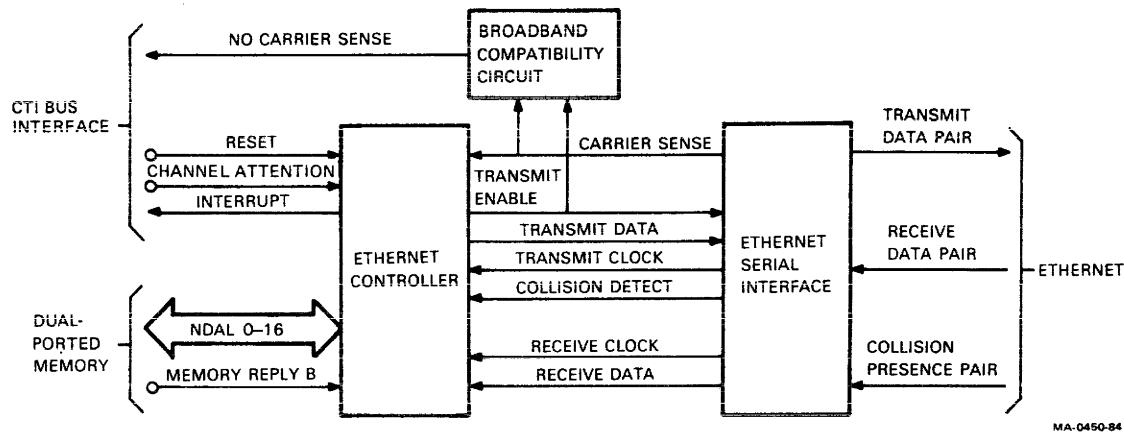

| 3.8     | Ethernet Interface .....                                                                        | 3-34 |

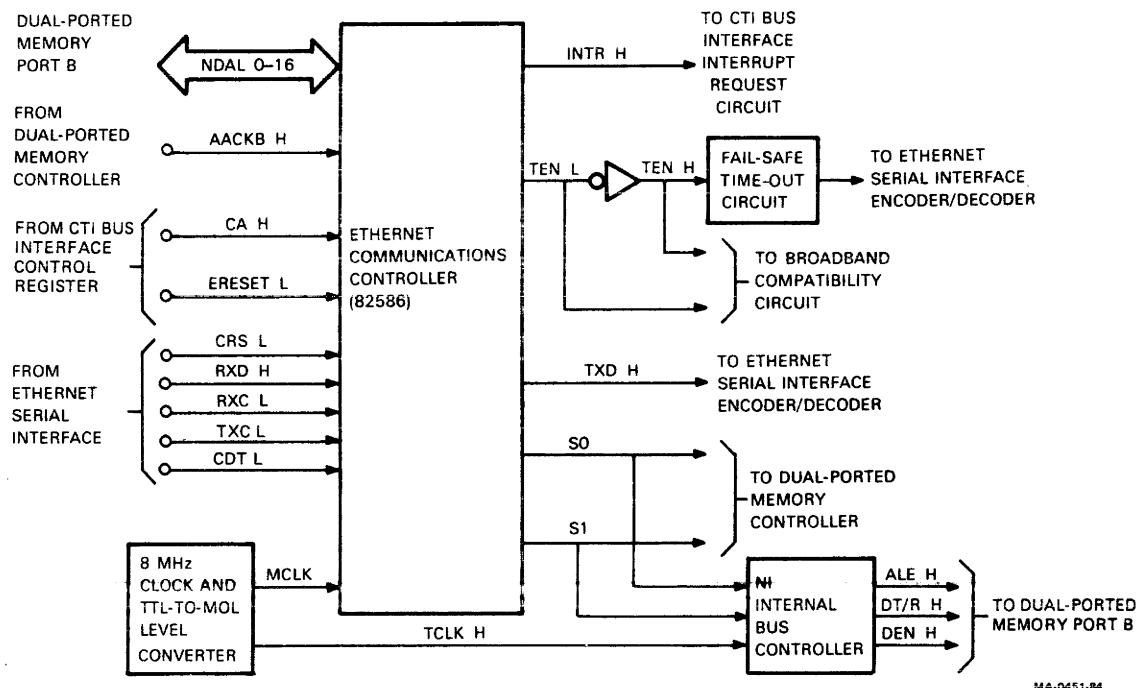

| 3.8.1   | Ethernet Controller .....                                                                       | 3-34 |

| 3.8.1.1 | Clock and TTL-to-MOS Level Converter .....                                                      | 3-34 |

| 3.8.1.2 | Ethernet Communications Controller Chip (82586) .....                                           | 3-34 |

| 3.8.1.3 | Fail-Safe Time-Out Circuit .....                                                                | 3-38 |

| 3.8.1.4 | NI Internal Bus Controller .....                                                                | 3-38 |

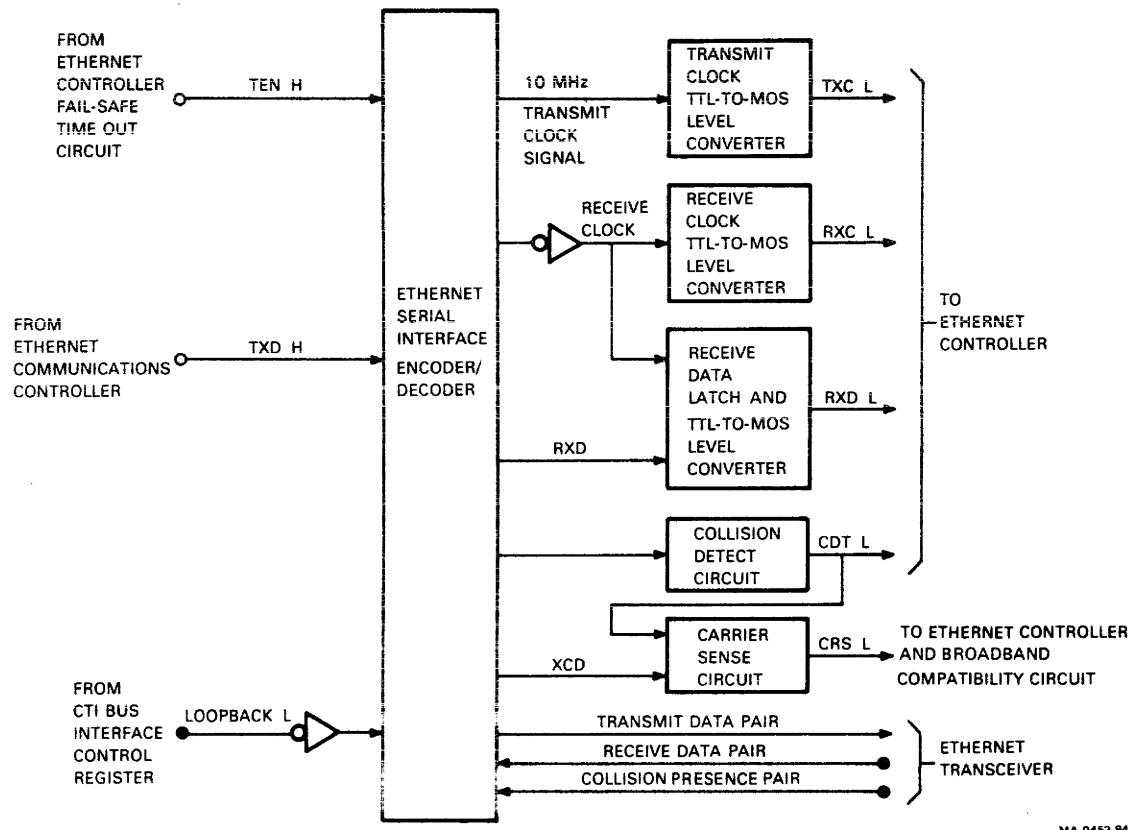

| 3.8.2   | Ethernet Serial Interface .....                                                                 | 3-38 |

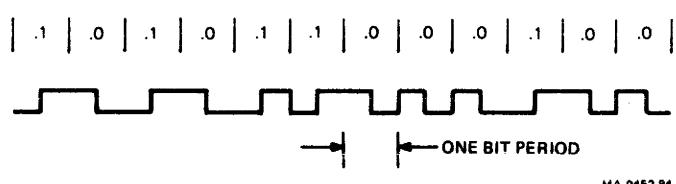

| 3.8.2.1 | Manchester Code .....                                                                           | 3-41 |

| 3.8.2.2 | Ethernet Serial Interface Encoder/Decoder .....                                                 | 3-42 |

| 3.8.2.3 | Transmit Clock TTL-to-MOS Level Converter .....                                                 | 3-42 |

| 3.8.2.4 | Receive Clock TTL-to-MOS Level Converter .....                                                  | 3-42 |

| 3.8.2.5 | Receive Data Resynchronizer and TTL-to-MOS Level Converter .....                                | 3-42 |

| 3.8.2.6 | Collision Clock Detect Circuit .....                                                            | 3-43 |

| 3.8.2.7 | Carrier Sense Circuit .....                                                                     | 3-43 |

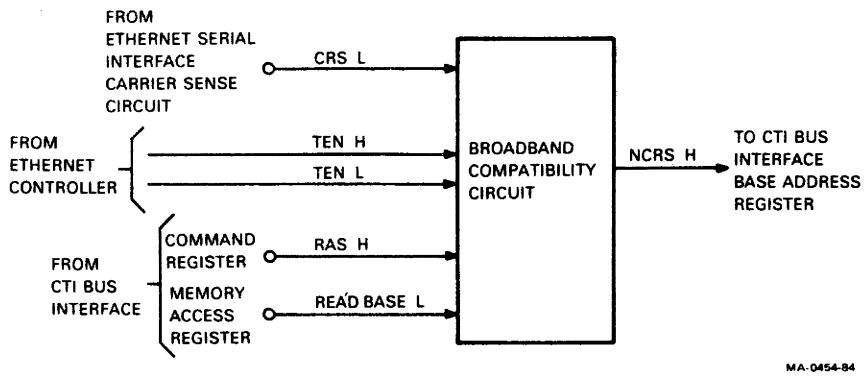

| 3.8.3   | Broadband Ethernet Compatibility Circuit .....                                                  | 3-43 |

## CHAPTER 4 PROFESSIONAL 380 EXTENDED BITMAP OPTION MODULE

|         |                                           |     |

|---------|-------------------------------------------|-----|

| 4.1     | Introduction .....                        | 4-1 |

| 4.2     | Functional Description .....              | 4-1 |

| 4.3     | Detailed Description .....                | 4-2 |

| 4.3.1   | Bus Interface Signals .....               | 4-3 |

| 4.3.2   | Video Signals .....                       | 4-4 |

| 4.3.3   | Interchip Control Signals .....           | 4-5 |

| 4.3.4   | Operational Power Levels .....            | 4-5 |

| 4.3.5   | EBO Module Connector Pin Assignment ..... | 4-6 |

| 4.4     | Hardware Specifications .....             | 4-6 |

| 4.4.1   | Physical Specifications .....             | 4-6 |

| 4.4.2   | Power Specifications .....                | 4-6 |

| 4.4.3   | Environmental Specifications .....        | 4-7 |

| 4.4.3.1 | Operating Environment .....               | 4-7 |

| 4.4.3.2 | Operating Temperature .....               | 4-7 |

| 4.4.3.3 | Operating Relative Humidity .....         | 4-7 |

| 4.4.3.4 | Storage Environment .....                 | 4-7 |

| 4.4.3.5 | Storage Temperature .....                 | 4-7 |

| 4.4.3.6 | Storage Relative Humidity .....           | 4-7 |

## CHAPTER 5 RD/RD52-A HARD DISK DRIVE CONTROLLER MODULE

|         |                                                               |      |

|---------|---------------------------------------------------------------|------|

| 5.1     | General Information .....                                     | 5-1  |

| 5.1.1   | Related Documentation .....                                   | 5-1  |

| 5.1.2   | Hard Disk Drive Controller Module .....                       | 5-2  |

| 5.2     | Functional Components .....                                   | 5-2  |

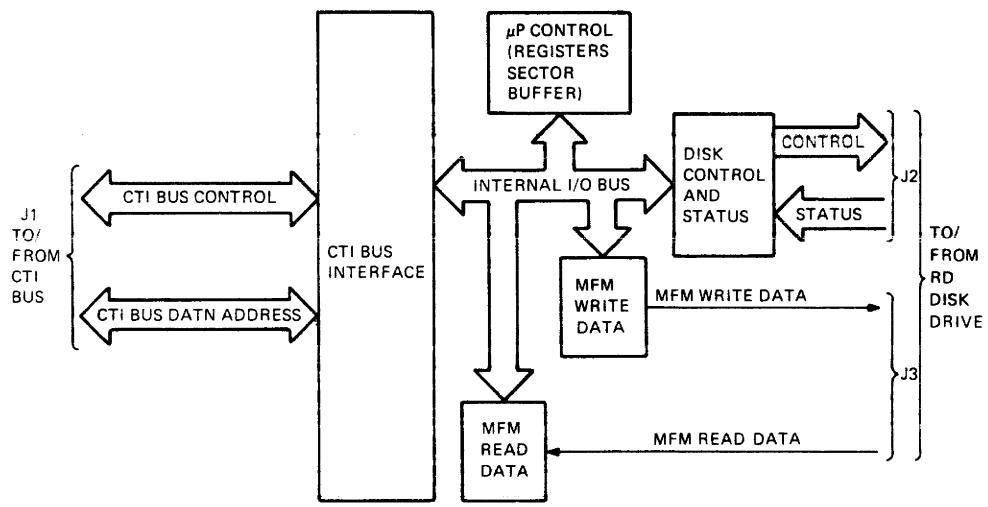

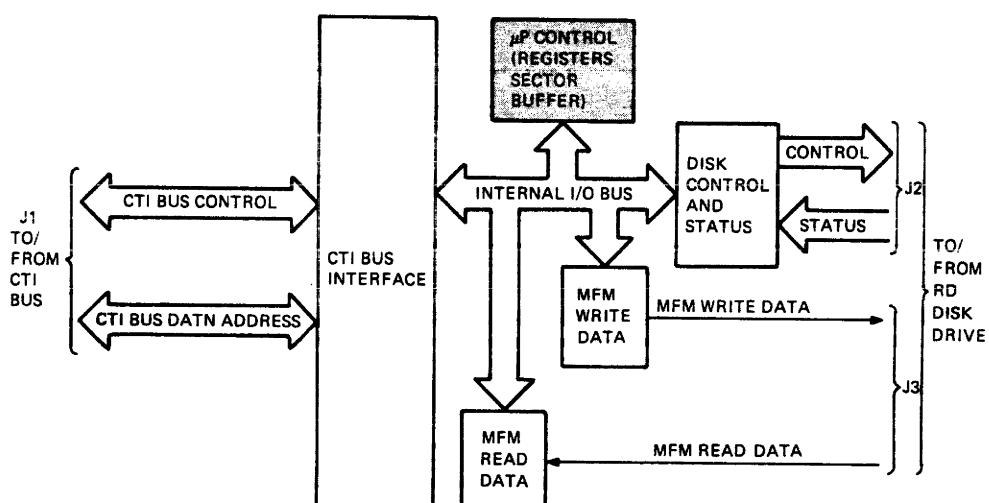

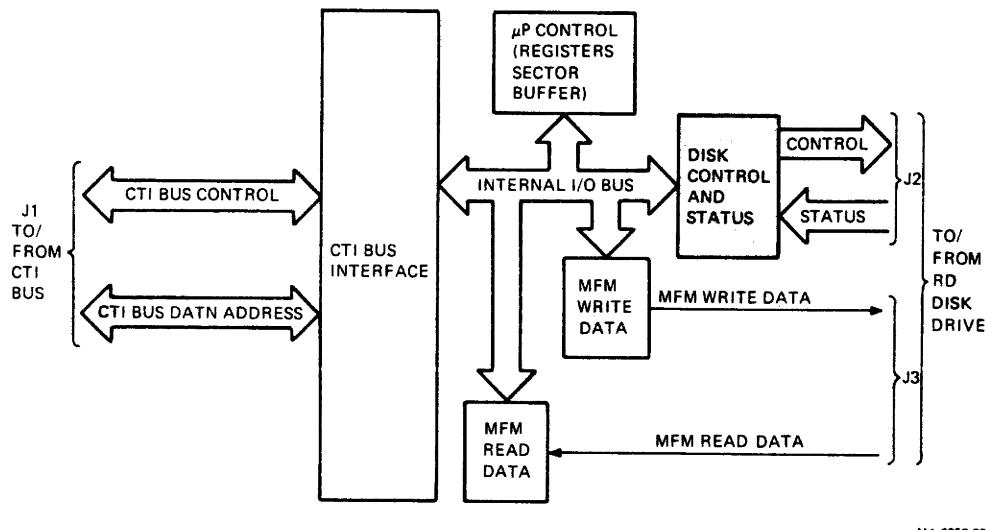

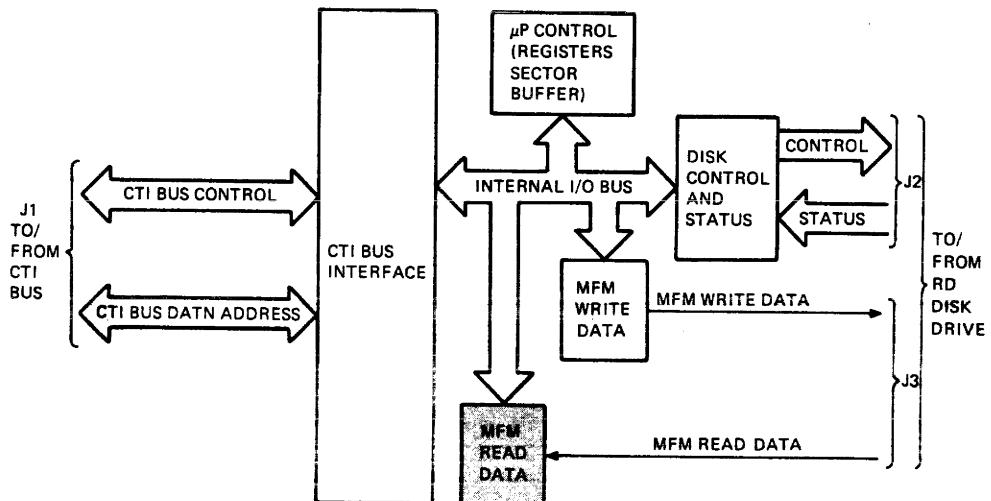

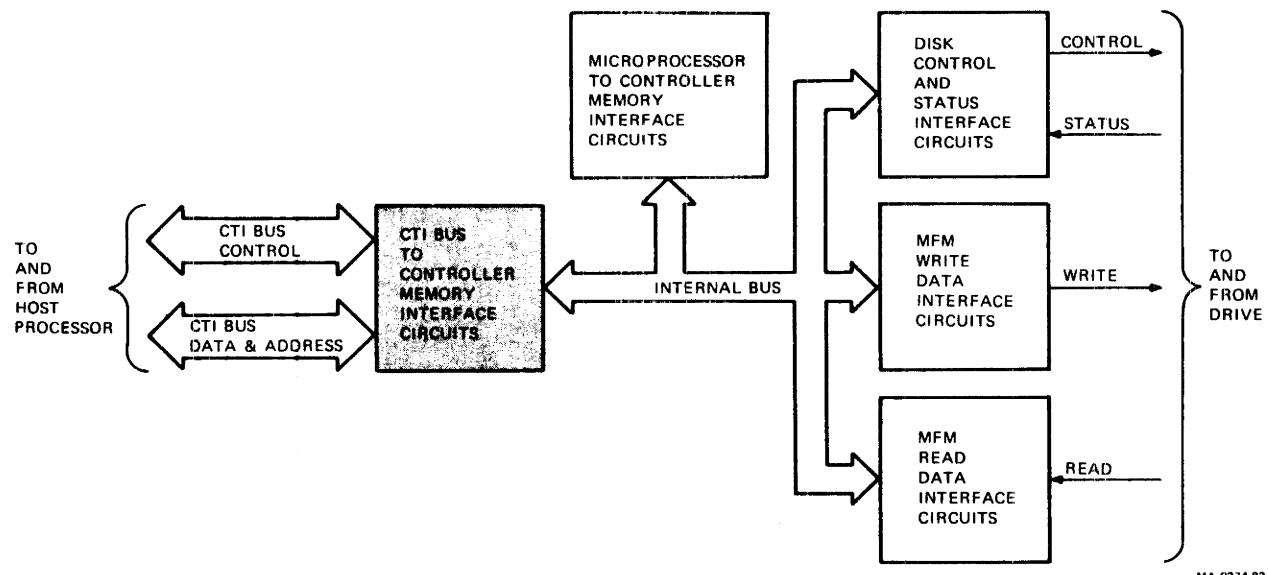

| 5.2.1   | Overview .....                                                | 5-2  |

| 5.2.2   | CTI Bus Interface Circuits .....                              | 5-4  |

| 5.2.3   | Microprocessor ( $\mu$ P) Control Circuits .....              | 5-4  |

| 5.2.4   | Disk Control and Status Circuits .....                        | 5-4  |

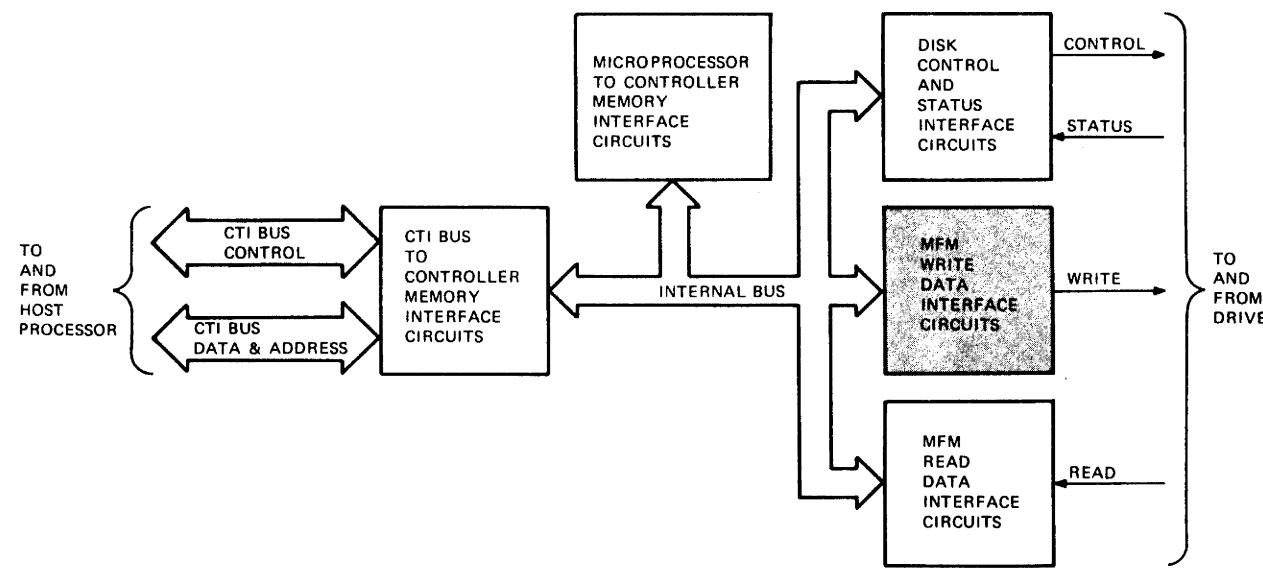

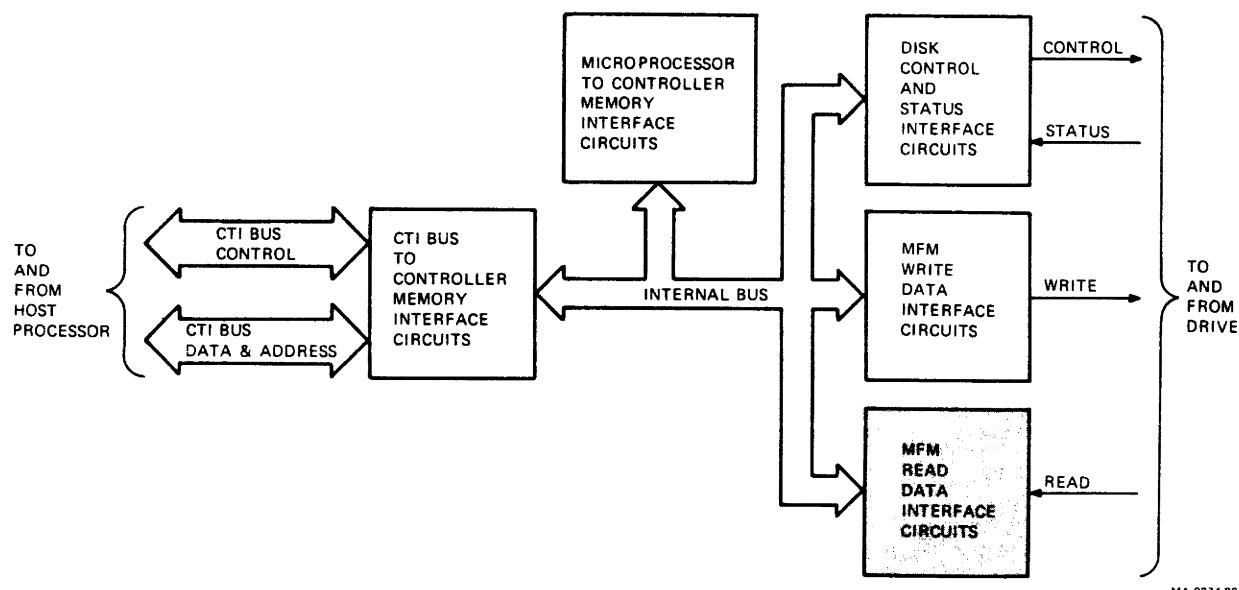

| 5.2.5   | Modified Frequency Modulation (MFM) Write Data Circuits ..... | 5-4  |

| 5.2.6   | Modified Frequency Modulation (MFM) Read Data Circuits .....  | 5-5  |

| 5.3     | Theory of Operation .....                                     | 5-5  |

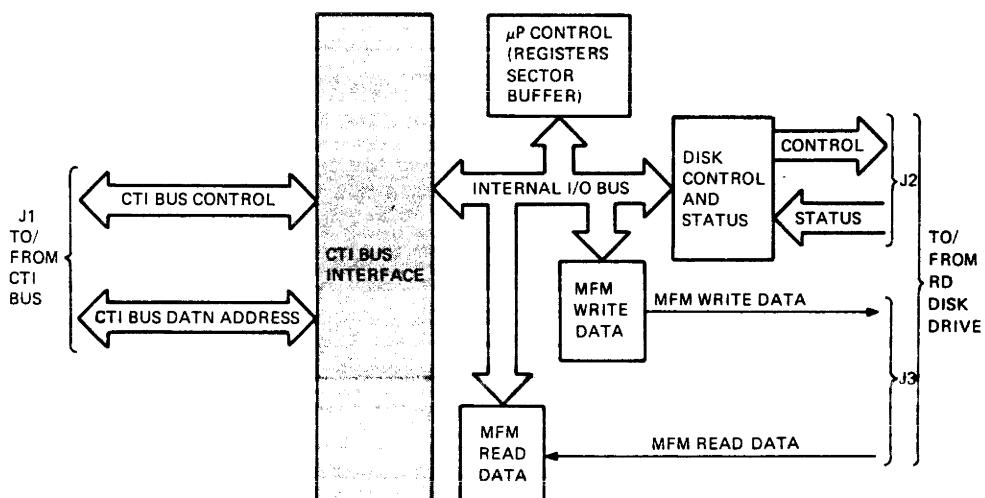

| 5.3.1   | CTI Bus Interface Circuits .....                              | 5-6  |

| 5.3.1.1 | CTI Bus I/O Controller .....                                  | 5-6  |

| 5.3.1.2 | CTI Bus Data/Address Transceivers .....                       | 5-6  |

| 5.3.1.3 | STATUS/INIT Register .....                                    | 5-6  |

| 5.3.1.4 | Address Buffer .....                                          | 5-6  |

| 5.3.1.5 | Data I/O Ports .....                                          | 5-6  |

| 5.3.1.6 | General Controller Module Access .....                        | 5-7  |

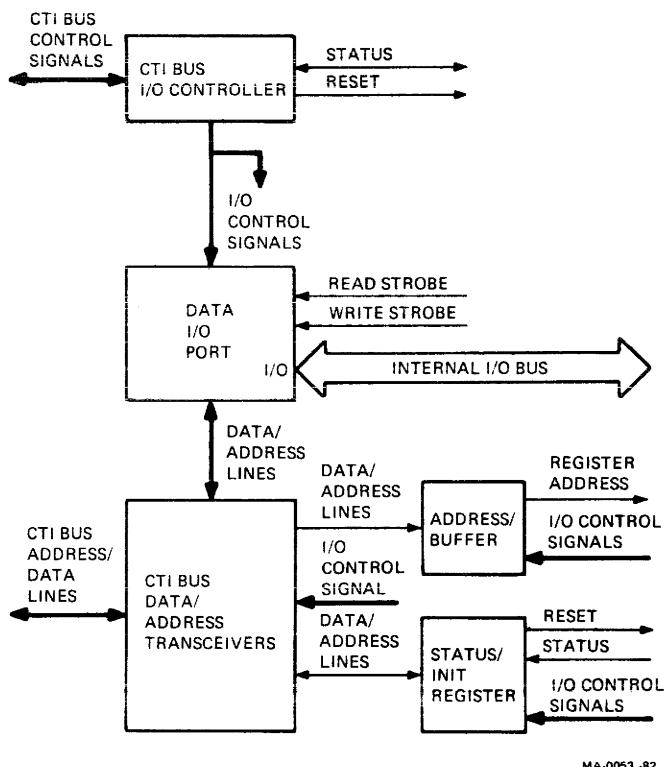

| 5.3.2   | $\mu$ P Control Circuits .....                                | 5-8  |

| 5.3.2.1 | Internal I/O Bus Control .....                                | 5-8  |

| 5.3.2.2 | Memory Mapping and Access .....                               | 5-8  |

| 5.3.2.3 | Disk Read/Write Control Buffer .....                          | 5-8  |

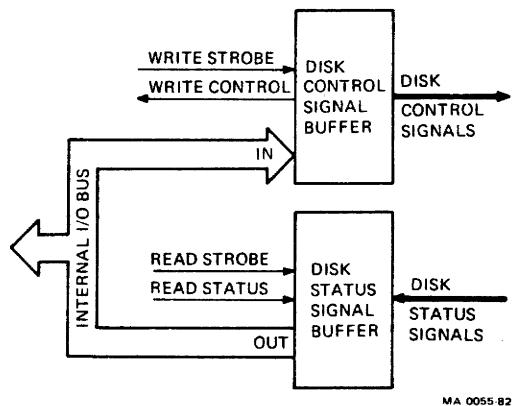

| 5.3.3   | Disk Control and Status Circuits .....                        | 5-10 |

|          |                                                   |      |

|----------|---------------------------------------------------|------|

| 5.3.3.1  | Disk Control Signal Buffer .....                  | 5-10 |

| 5.3.3.2  | Disk Status Signal Buffer .....                   | 5-10 |

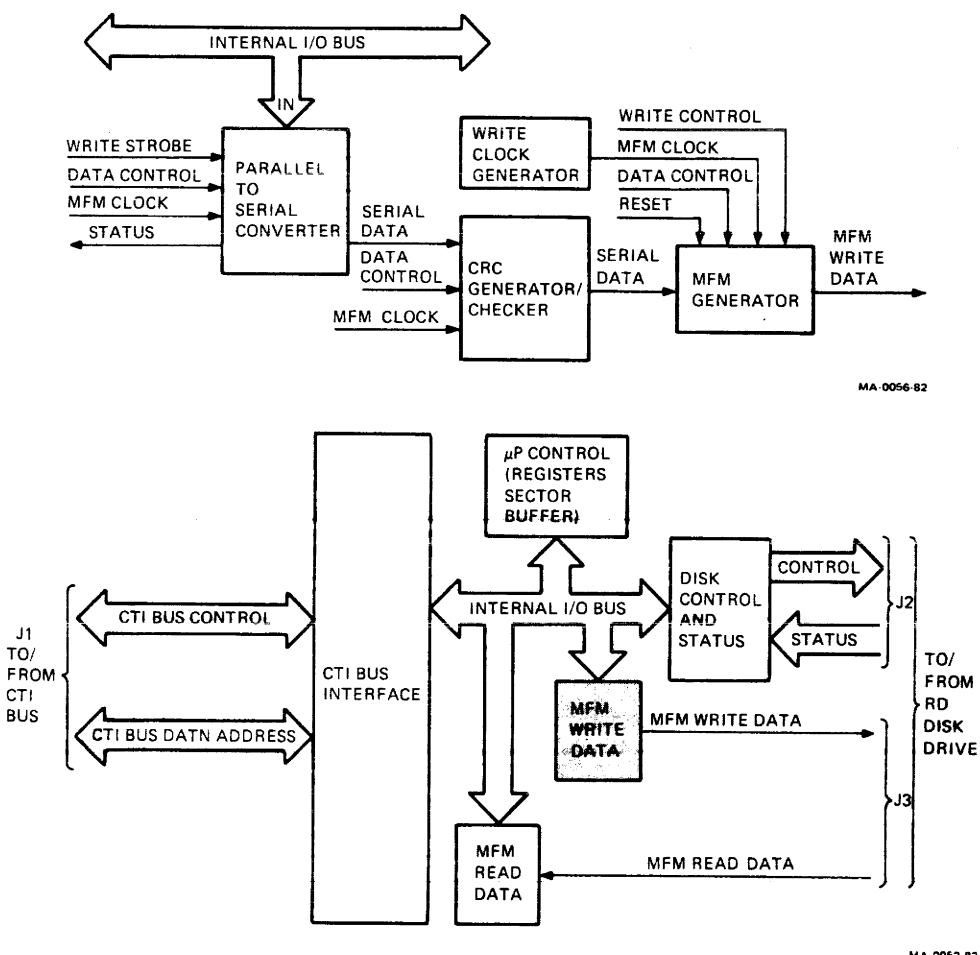

| 5.3.4    | MFM Write Data Circuits .....                     | 5-10 |

| 5.3.4.1  | Parallel-to-Serial Converter .....                | 5-12 |

| 5.3.4.2  | CRC Generator/Checker .....                       | 5-12 |

| 5.3.4.3  | MFM Generator .....                               | 5-12 |

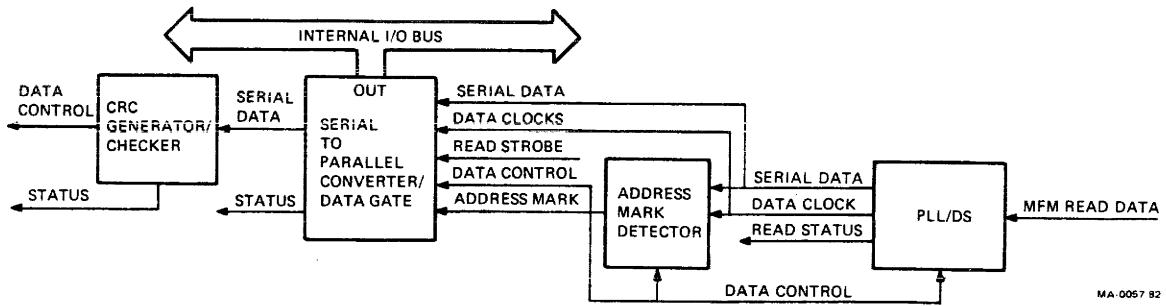

| 5.3.5    | MFM Read Data Circuits .....                      | 5-12 |

| 5.3.5.1  | Phase Lock Loop/Data Separator .....              | 5-12 |

| 5.3.5.2  | Address Mark Detector .....                       | 5-12 |

| 5.3.5.3  | Serial-to-Parallel Converter .....                | 5-13 |

| 5.3.5.4  | CRC Generator/Checker .....                       | 5-13 |

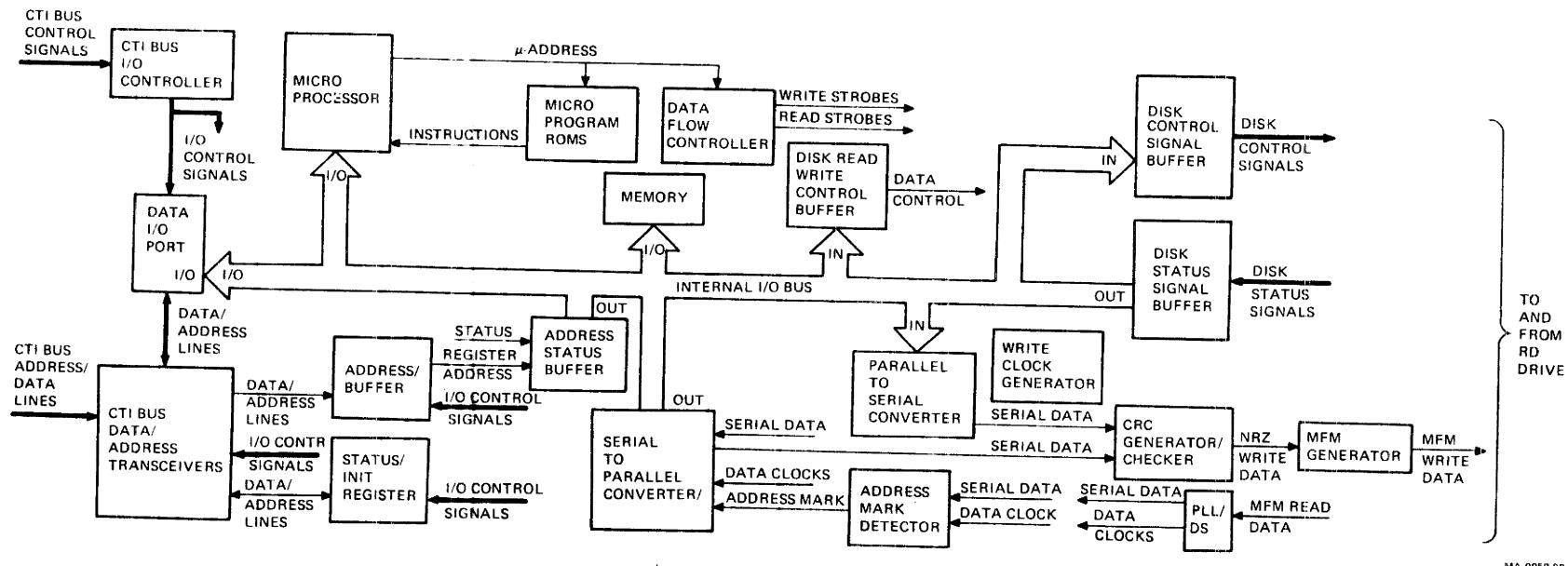

| 5.3.6    | Controller Data Flow Description .....            | 5-14 |

| 5.3.6.1  | Drive Command Data Flow .....                     | 5-14 |

| 5.3.6.2  | Write Data Flow .....                             | 5-14 |

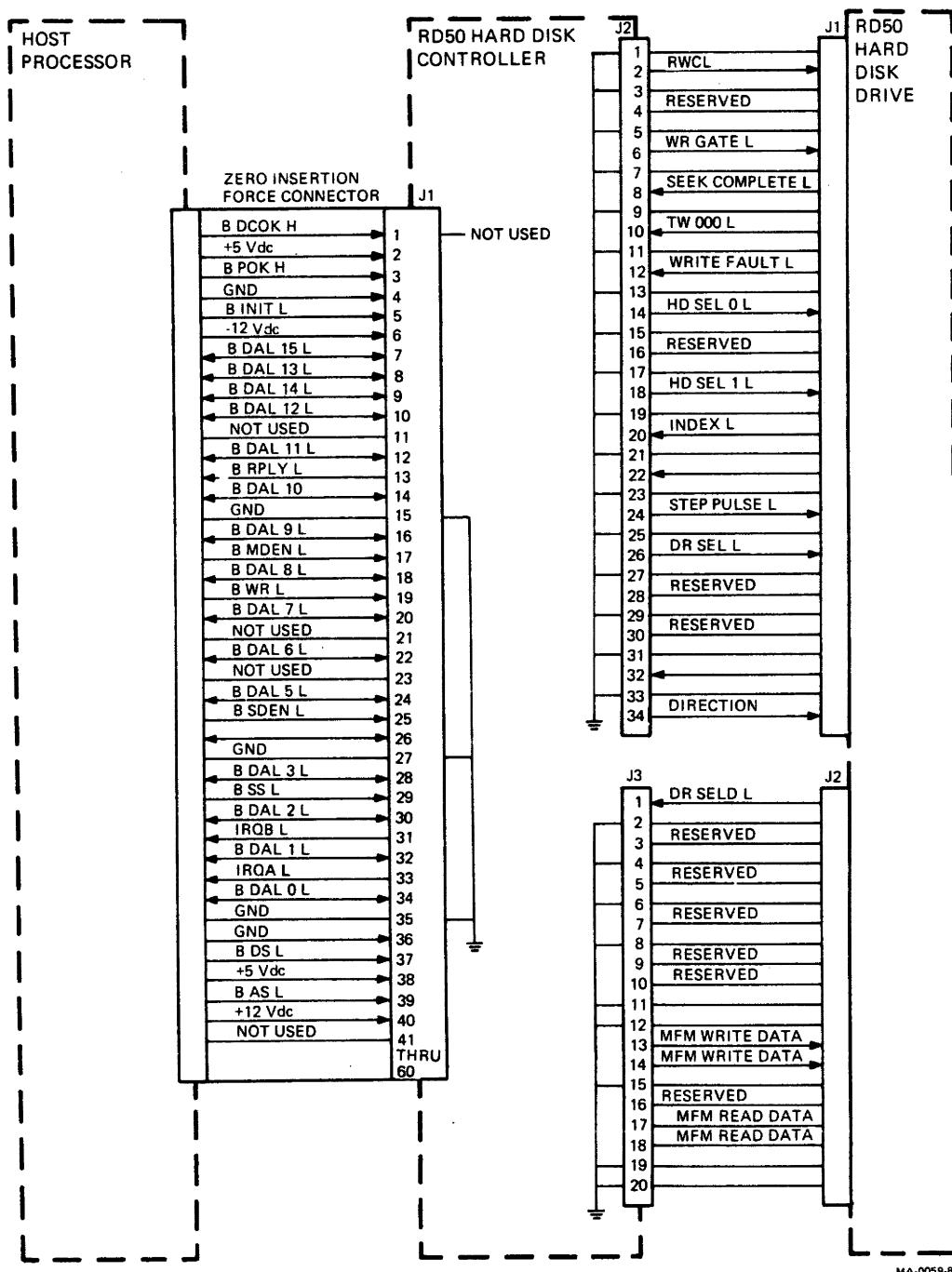

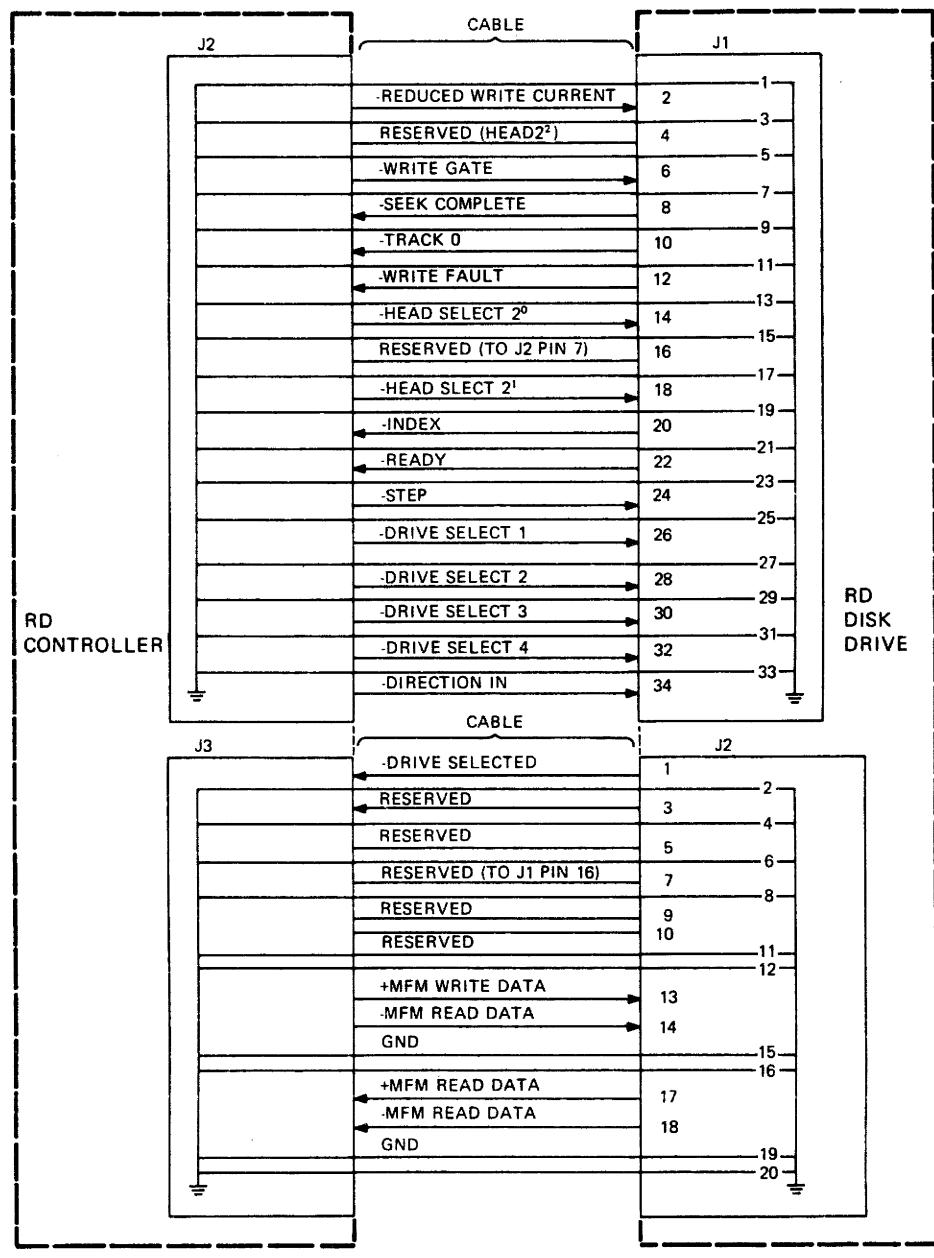

| 5.4      | Detailed Connector Descriptions .....             | 5-16 |

| 5.4.1    | CTI Bus Interface J1 .....                        | 5-17 |

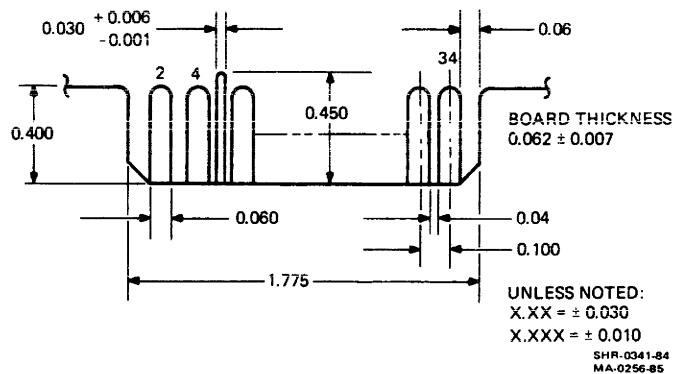

| 5.4.2    | Disk Control/Status Connector J2 .....            | 5-16 |

| 5.4.2.1  | REDUCED WRITE CURRENT (Pin 2) .....               | 5-18 |

| 5.4.2.2  | WRITE GATE (Pin 6) .....                          | 5-18 |

| 5.4.2.3  | HEAD SELECT (Pin 4, 14 and 18) .....              | 5-18 |

| 5.4.2.4  | STEP (Pin 24) .....                               | 5-18 |

| 5.4.2.5  | DIRECTION IN (Pin 34) .....                       | 5-18 |

| 5.4.2.6  | DRIVE SELECT (Pin 26) .....                       | 5-18 |

| 5.4.2.7  | SEEK COMPLETE (Pin 8) .....                       | 5-18 |

| 5.4.2.8  | TRACK 000 (Pin 10) .....                          | 5-18 |

| 5.4.2.9  | WRITE FAULT (Pin 12) .....                        | 5-18 |

| 5.4.2.10 | INDEX (Pin 20) .....                              | 5-18 |

| 5.4.2.11 | READY (Pin 22) .....                              | 5-19 |

| 5.4.2.12 | RD50 5 MB (Pin 32) .....                          | 5-19 |

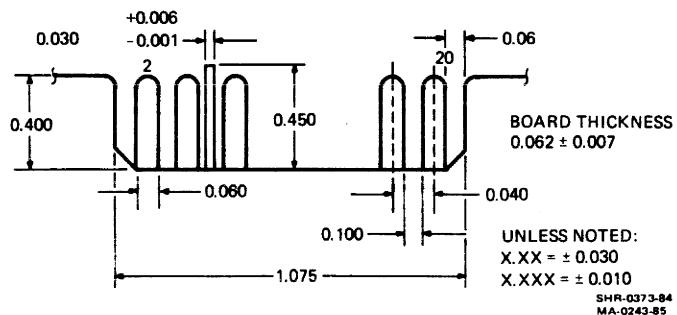

| 5.4.3    | Disk Data I/O Connector J3 .....                  | 5-19 |

| 5.4.3.1  | DRIVE SELECTED (Pin 1) .....                      | 5-19 |

| 5.4.3.2  | MFM WRITE DATA (Pins 13 and 14) .....             | 5-19 |

| 5.4.3.3  | MFM READ DATA (Pins 17 and 18) .....              | 5-19 |

| 5.5      | Programming Registers .....                       | 5-20 |

| 5.5.1    | ID Register (774000) .....                        | 5-20 |

| 5.5.2    | ERROR/PRECOMP Register (774004) .....             | 5-21 |

| 5.5.2.1  | DM Not Found (Bit 8) .....                        | 5-21 |

| 5.5.2.2  | TR000 Error (Bit 9) .....                         | 5-21 |

| 5.5.2.3  | Illegal/Aborted Command (Bit 10) .....            | 5-22 |

| 5.5.2.4  | ID Not Found (Bit 12) .....                       | 5-22 |

| 5.5.2.5  | CRC Error ID Field (Bit 13) .....                 | 5-22 |

| 5.5.2.6  | CRC Error Data Field (Bit 14) .....               | 5-22 |

| 5.5.3    | BACKUP REVISION/SECTOR ID Register (774006) ..... | 5-22 |

| 5.5.4    | DATA BUFFER Register (774010) .....               | 5-23 |

| 5.5.5    | CYLINDER ID Register (774012) .....               | 5-24 |

| 5.5.6    | HEAD ID Register (774014) .....                   | 5-24 |

| 5.5.7    | STA 2/COMMAND Register (774016) .....             | 5-24 |

| 5.5.7.1  | Restore .....                                     | 5-24 |

| 5.5.7.2  | Read Sector .....                                 | 5-26 |

|         |                                                          |      |

|---------|----------------------------------------------------------|------|

| 5.5.7.3 | Write Sector .....                                       | 5-27 |

| 5.5.7.4 | Format .....                                             | 5-27 |

| 5.5.7.5 | Error Status .....                                       | 5-28 |

| 5.5.7.6 | Data Request .....                                       | 5-28 |

| 5.5.7.7 | Seek Complete .....                                      | 5-28 |

| 5.5.7.8 | Write Fault .....                                        | 5-28 |

| 5.5.7.9 | Disk Drive Ready .....                                   | 5-28 |

| 5.5.8   | STATUS/INIT Register (774020) .....                      | 5-29 |

| 5.5.8.1 | OP ENDED .....                                           | 5-29 |

| 5.5.8.2 | RESET/INITIALIZE .....                                   | 5-29 |

| 5.5.8.3 | DRQ .....                                                | 5-29 |

| 5.5.8.4 | BUSY .....                                               | 5-29 |

| 5.6     | General Sequence of Operation .....                      | 5-30 |

| 5.6.1   | Read Sector, Write Sector, Format Command .....          | 5-30 |

| 5.6.1.1 | Read Sector Command Follow-up Sequence .....             | 5-30 |

| 5.6.1.2 | Write Sector and Format Command Preparation .....        | 5-30 |

| 5.6.1.3 | Write Sector and Format Command Follow-up Sequence ..... | 5-30 |

| 5.6.2   | Read After Write Verify Follow-up Sequence .....         | 5-31 |

| 5.6.3   | Restore Command .....                                    | 5-31 |

| 5.6.4   | Initialization Sequence .....                            | 5-31 |

| 5.7     | Specifications .....                                     | 5-32 |

| 5.7.1   | Environmental .....                                      | 5-32 |

| 5.7.2   | Power .....                                              | 5-32 |

## CHAPTER 6 RD50/RD51 HARD DISK DRIVE

|         |                                                         |      |

|---------|---------------------------------------------------------|------|

| 6.1     | General Information .....                               | 6-1  |

| 6.1.1   | Related Documentation .....                             | 6-1  |

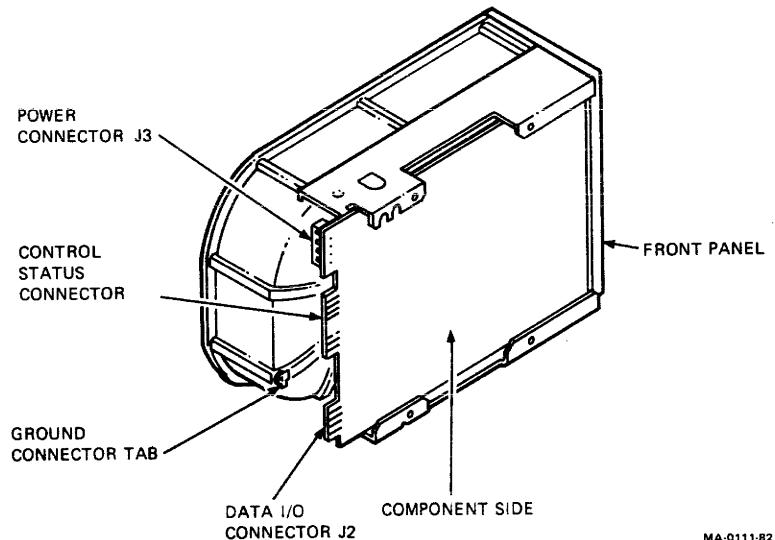

| 6.1.2   | Hard Disk Drive .....                                   | 6-2  |

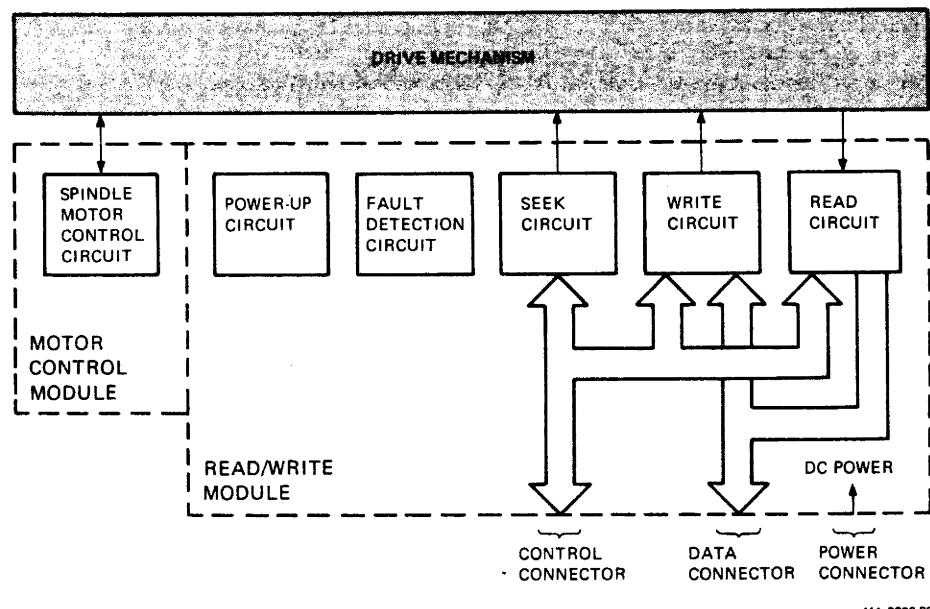

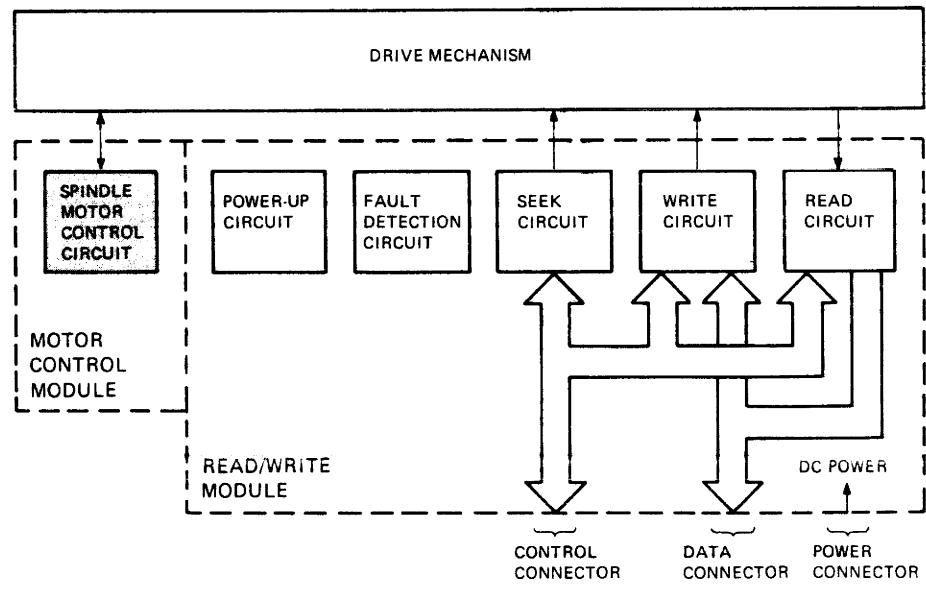

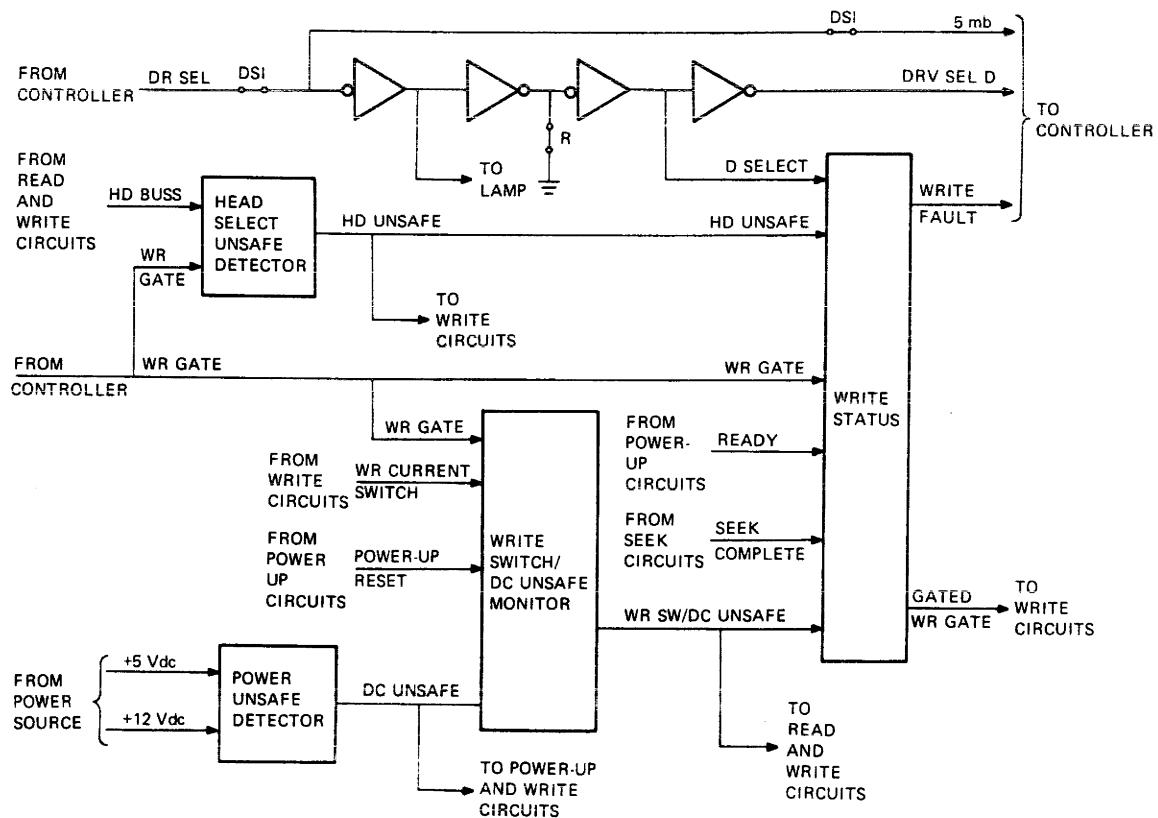

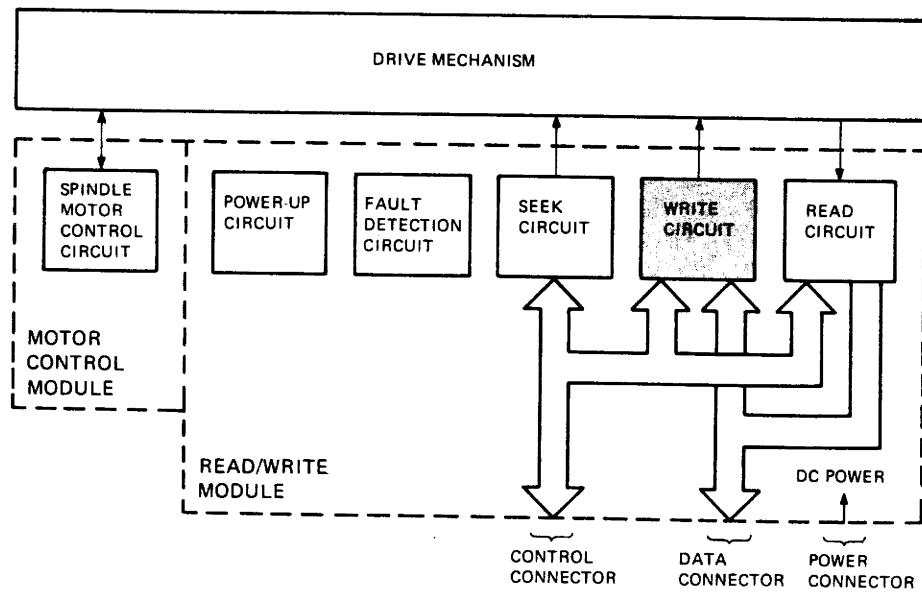

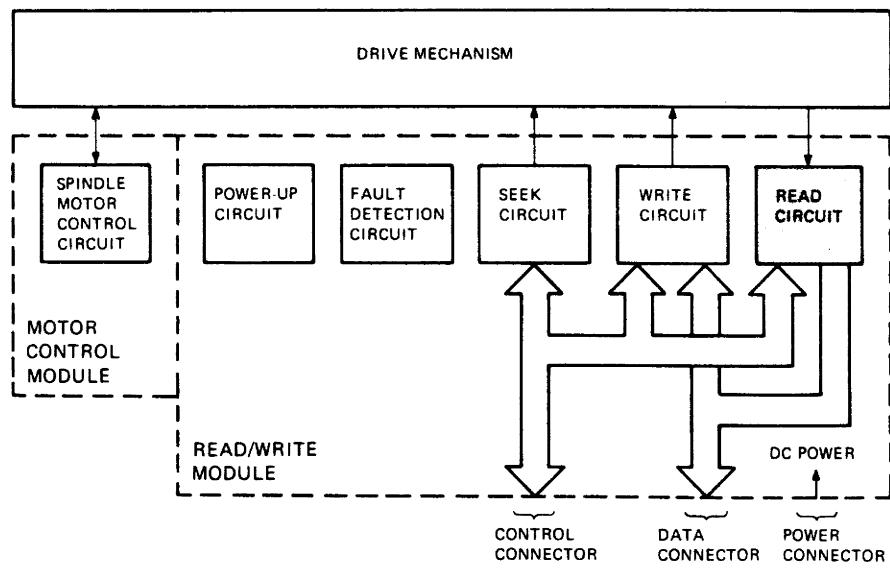

| 6.2     | Functional Components .....                             | 6-2  |

| 6.2.1   | Overview .....                                          | 6-2  |

| 6.2.2   | Drive Mechanism .....                                   | 6-2  |

| 6.2.3   | Spindle Motor Control Circuit .....                     | 6-2  |

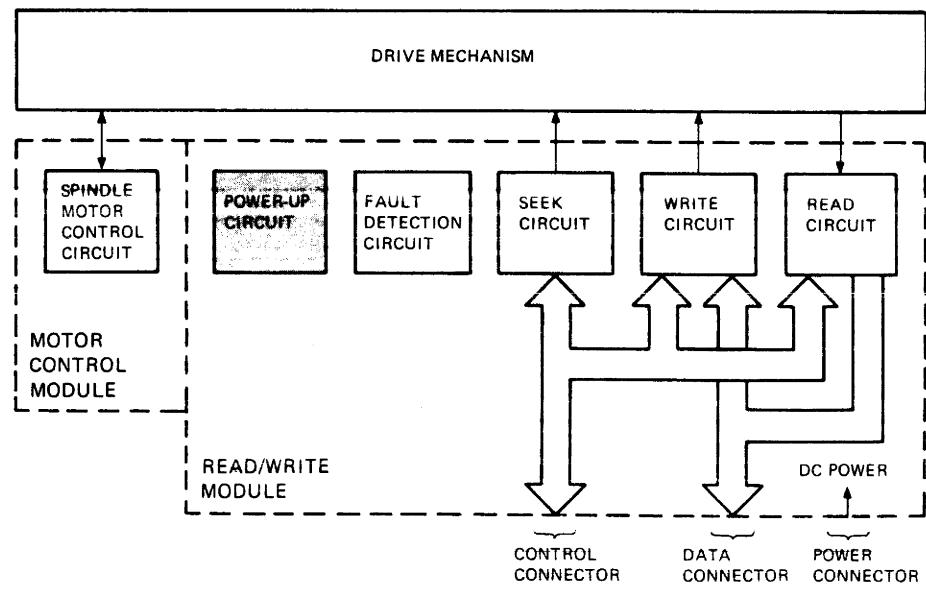

| 6.2.4   | Power-Up Circuit .....                                  | 6-3  |

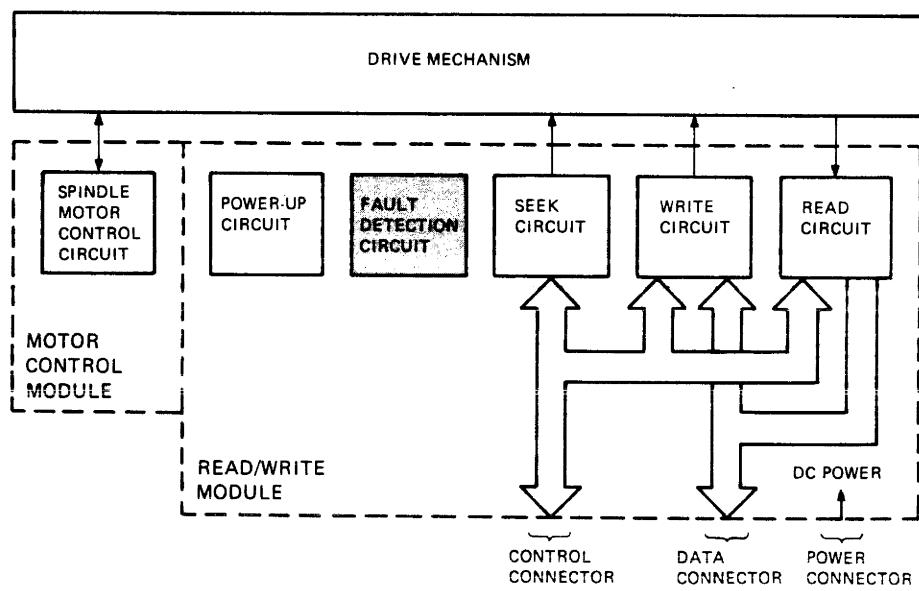

| 6.2.5   | Fault Detection Circuit .....                           | 6-3  |

| 6.2.6   | Seek Circuit .....                                      | 6-3  |

| 6.2.7   | Write Circuit .....                                     | 6-4  |

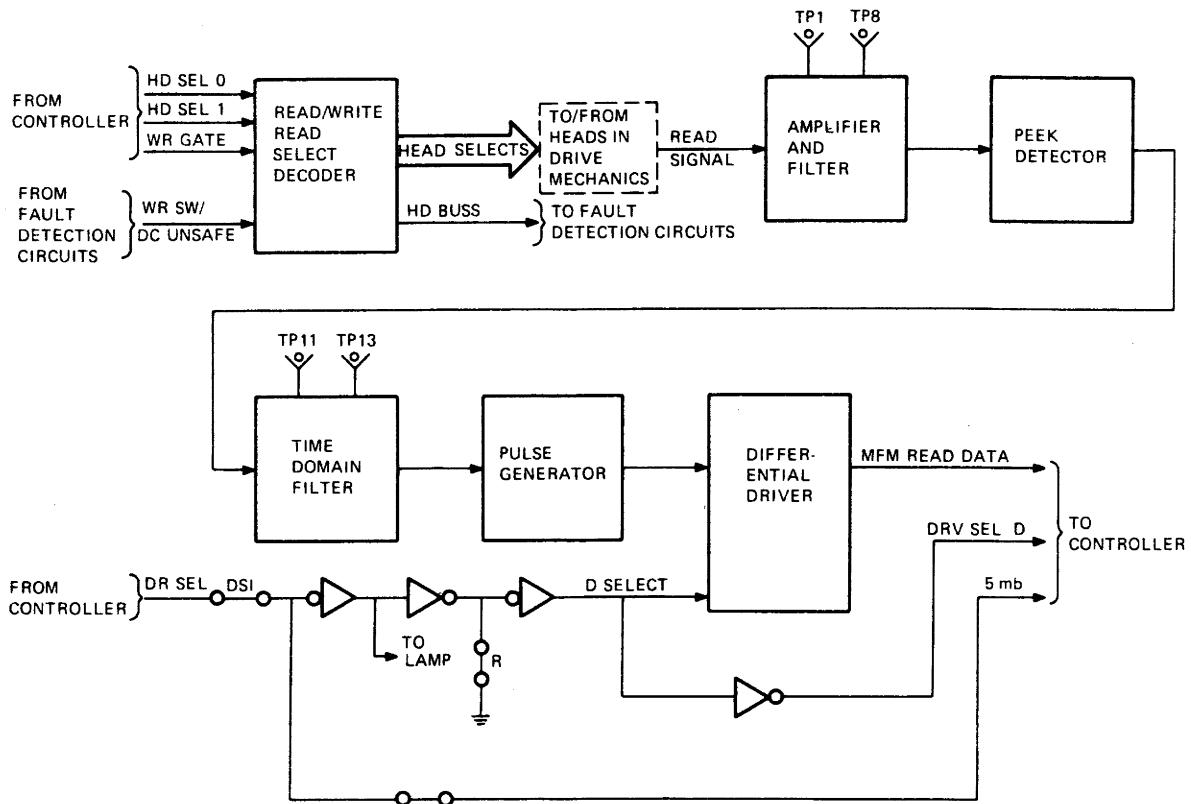

| 6.2.8   | Read Circuit .....                                      | 6-4  |

| 6.3     | Theory of Operation .....                               | 6-4  |

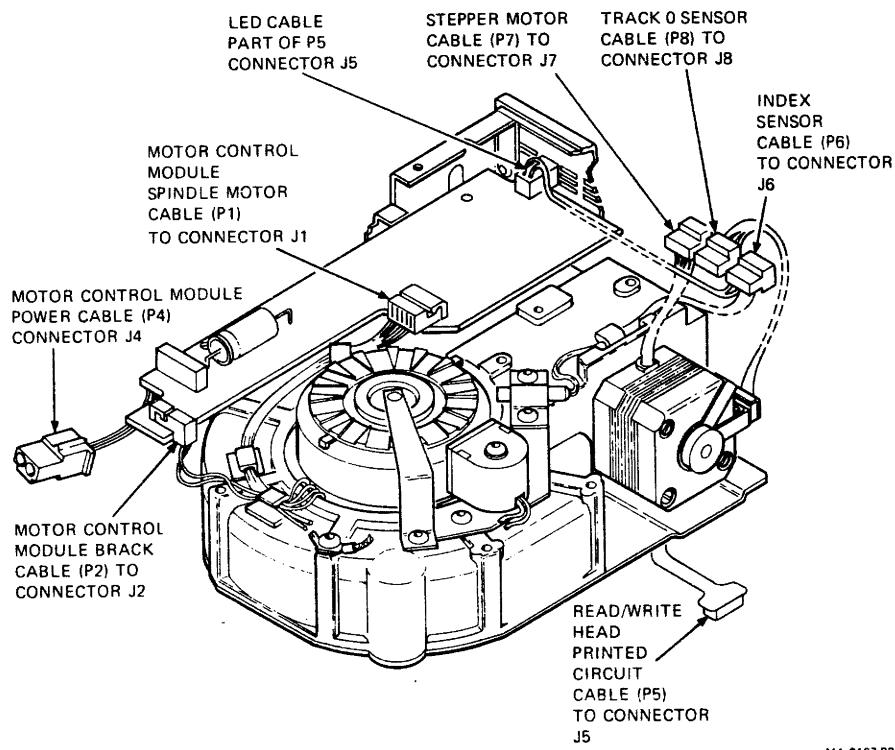

| 6.3.1   | Drive Mechanism Detailed Operations .....               | 6-4  |

| 6.3.1.1 | Sealed Head and Disk Assembly (HDA) .....               | 6-4  |

| 6.3.1.2 | Sensors and Hardware .....                              | 6-9  |

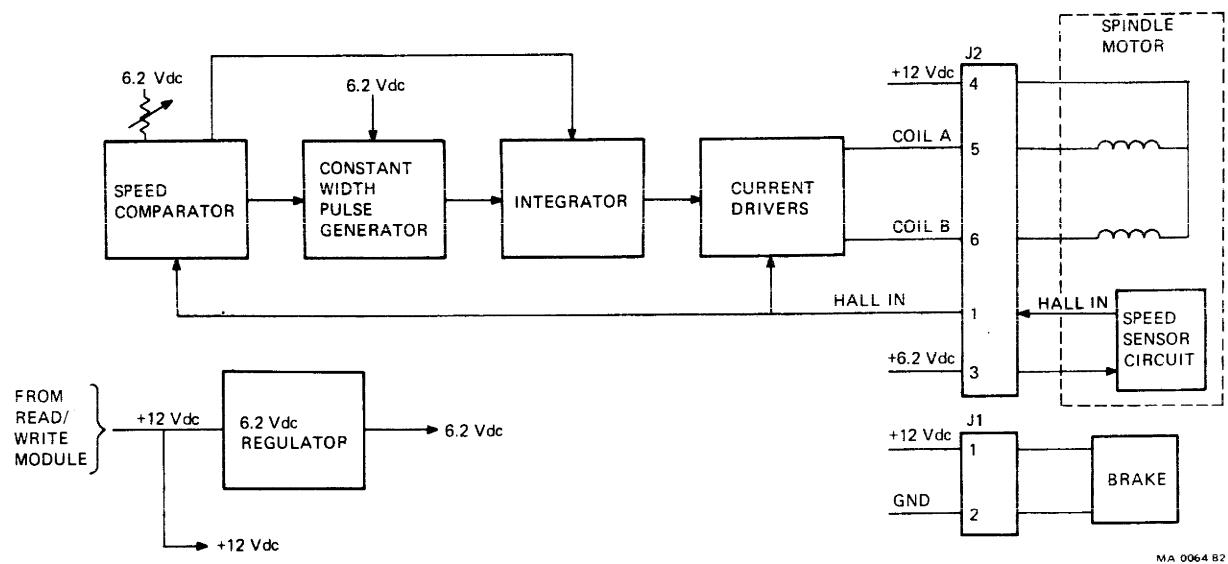

| 6.3.2   | Spindle Motor Control Circuit Detailed Operations ..... | 6-10 |

| 6.3.2.1 | Motor Current Control .....                             | 6-10 |

| 6.3.2.2 | Spindle Motor Current Switching .....                   | 6-12 |

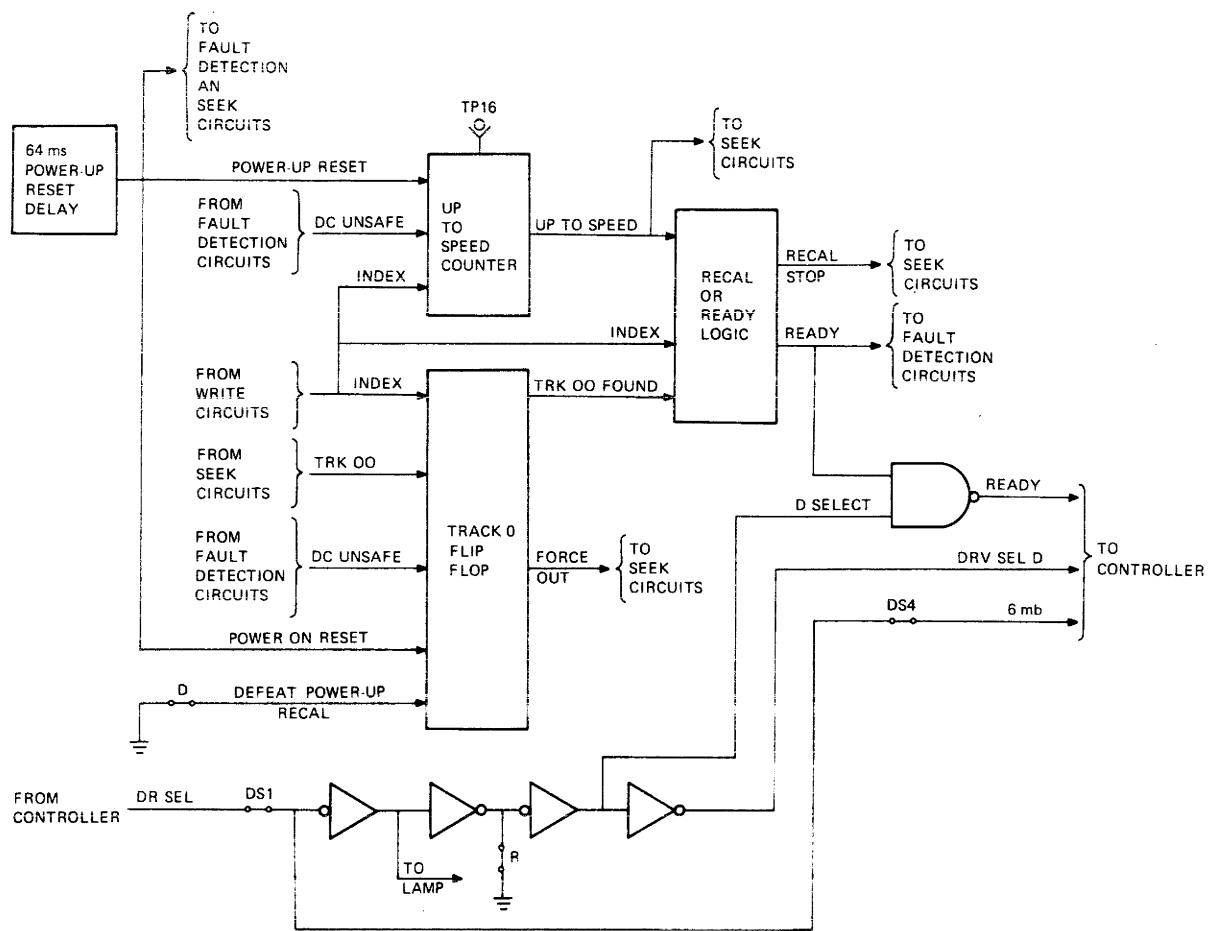

| 6.3.3   | Power-up Circuit Detailed Operations .....              | 6-12 |

| 6.3.3.1 | Reset Signal Generation .....                           | 6-12 |

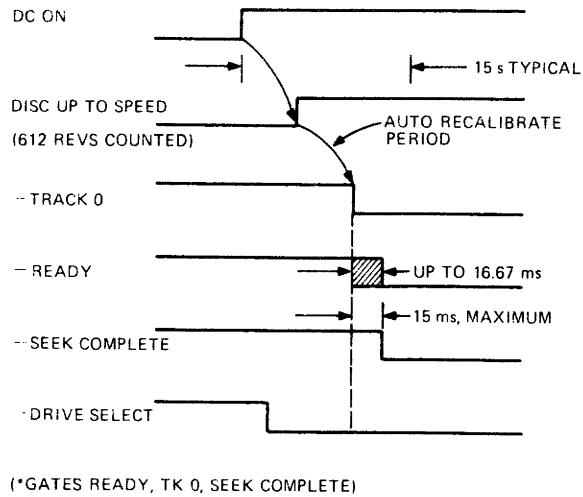

| 6.3.3.2 | Up to Speed Signal Generation .....                     | 6-12 |

| 6.3.3.3 | Recalibration Signal Generation .....                   | 6-14 |

|          |                                                   |      |

|----------|---------------------------------------------------|------|

| 6.3.3.4  | Ready Signal Generation .....                     | 6-14 |

| 6.3.3.5  | Recalibration Signal Generation Deselection ..... | 6-14 |

| 6.3.4    | Fault Detection Circuit Detailed Operation .....  | 6-14 |

| 6.3.4.1  | Head Selection Malfunction Detection .....        | 6-16 |

| 6.3.4.2  | Power Unsafe Detection .....                      | 6-16 |

| 6.3.4.3  | Write Circuit Unsafe Detection .....              | 6-16 |

| 6.3.4.4  | Write Status Detection .....                      | 6-16 |

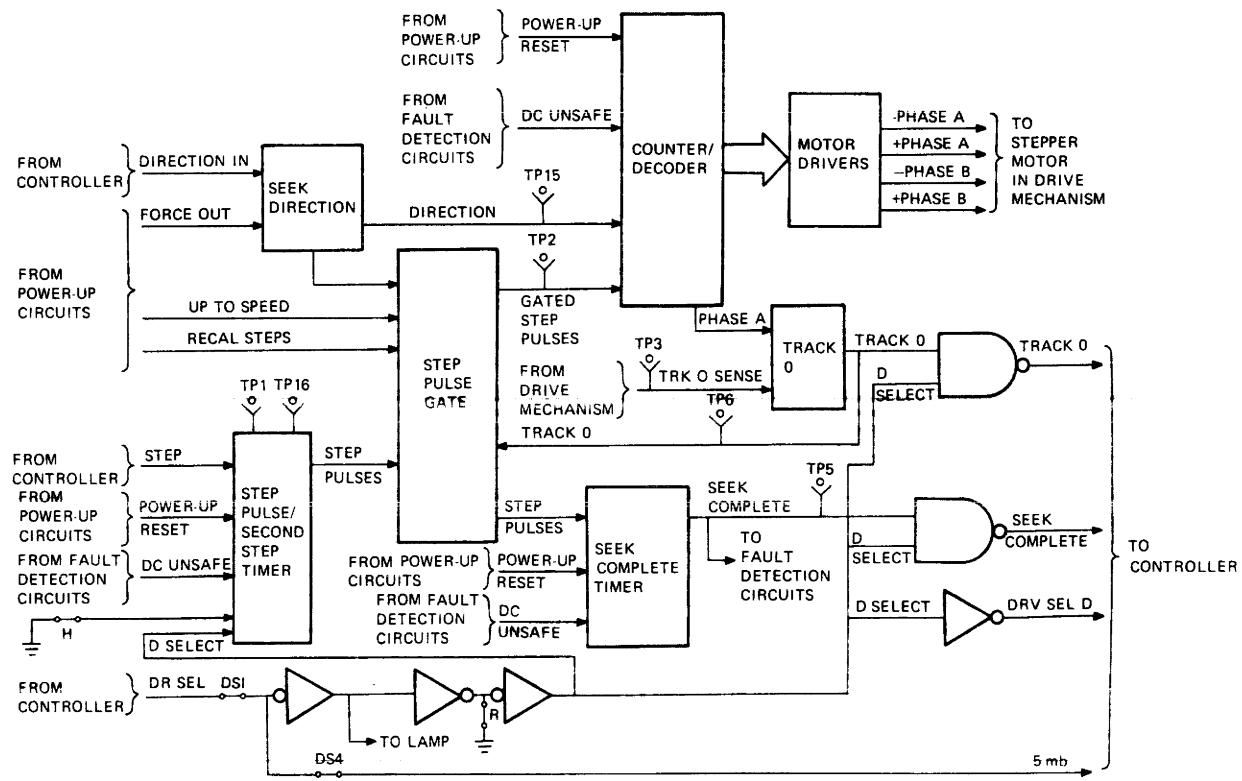

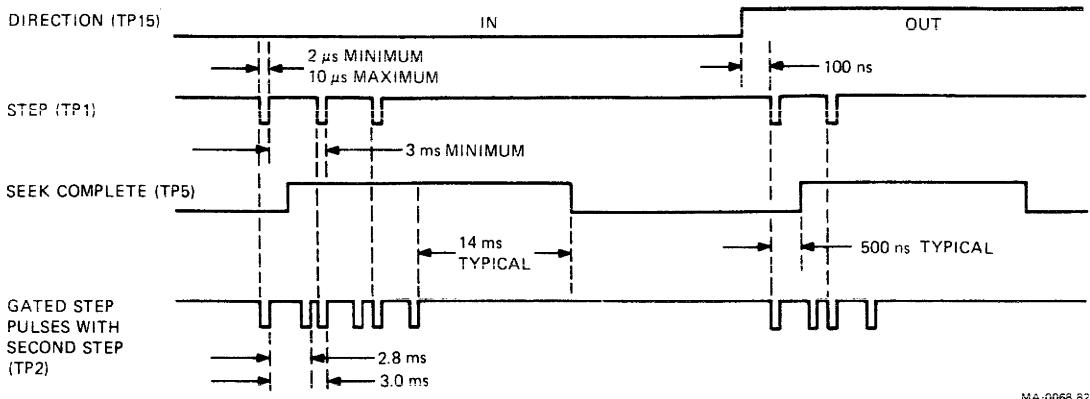

| 6.3.5    | Seek Circuit Detailed Operation .....             | 6-17 |

| 6.3.5.1  | Head Direction Selection .....                    | 6-18 |

| 6.3.5.2  | Step Pulse Selection .....                        | 6-18 |

| 6.3.5.3  | Step Pulse and Direction Signal Conversion .....  | 6-18 |

| 6.3.5.4  | Track 0 Monitoring .....                          | 6-18 |

| 6.3.5.5  | Seek Complete Indicator .....                     | 6-19 |

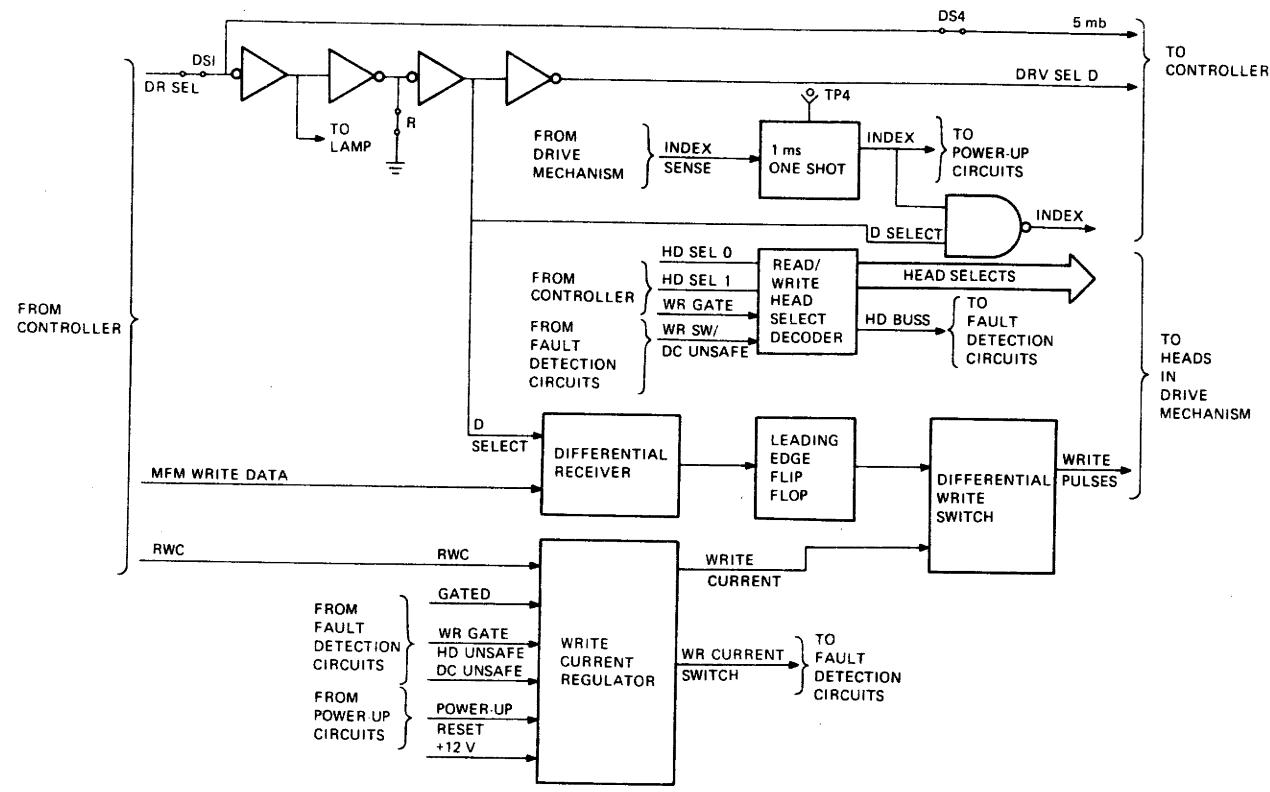

| 6.3.6    | Write Circuit Detailed Description .....          | 6-19 |

| 6.3.7    | Read Circuit Detailed Description .....           | 6-21 |

| 6.4      | Connector Descriptions .....                      | 6-24 |

| 6.4.1    | Connector J1, Read/Write Module .....             | 6-24 |

| 6.4.1.1  | REDUCED WRITE CURRENT (Pin 2) .....               | 6-26 |

| 6.4.1.2  | WRITE GATE (Pin 6) .....                          | 6-26 |

| 6.4.1.3  | SEEK COMPLETE (Pin 8) .....                       | 6-26 |

| 6.4.1.4  | TRACK 000 (Pin 10) .....                          | 6-26 |

| 6.4.1.5  | WRITE FAULT (Pin 12) .....                        | 6-26 |

| 6.4.1.6  | HEAD SELECT (Pin 14 and 18) .....                 | 6-26 |

| 6.4.1.7  | INDEX (Pin 20) .....                              | 6-26 |

| 6.4.1.8  | READY (Pin 22) .....                              | 6-26 |

| 6.4.1.9  | STEP (Pin 24) .....                               | 6-26 |

| 6.4.1.10 | DRIVE SELECT (Pin 26) .....                       | 6-26 |

| 6.4.1.11 | DRIVE CAPACITY (Pin 32) .....                     | 6-27 |

| 6.4.1.12 | DIRECTION IN (Pin 34) .....                       | 6-27 |

| 6.4.2    | Connector J2, Read/Write Module .....             | 6-27 |

| 6.4.2.1  | DRIVE SELECTED (Pin 1) .....                      | 6-27 |

| 6.4.2.2  | MFM WRITE DATA (Pins 13 and 14) .....             | 6-27 |

| 6.4.2.3  | MFM READ DATA (Pins 17 and 18) .....              | 6-28 |

| 6.4.3    | Connector J3, Read/Write Module .....             | 6-28 |

| 6.4.4    | Connector J4, Read/Write Module .....             | 6-28 |

| 6.4.5    | Connector J5, Read/Write Module .....             | 6-28 |

| 6.4.6    | Connector J6, Read/Write Module .....             | 6-28 |

| 6.4.7    | Connector J7, Read/Write Module .....             | 6-30 |

| 6.4.8    | Connector J8, Read/Write Module .....             | 6-30 |

| 6.4.9    | Connector J1, Motor Control Module .....          | 6-30 |

| 6.4.10   | Connector J2, Motor Control Module .....          | 6-30 |

| 6.5      | Maintenance Procedures .....                      | 6-31 |

| 6.5.1    | Preventive Maintenance .....                      | 6-31 |

| 6.5.2    | Test Point Locations .....                        | 6-31 |

| 6.5.3    | Jumper/Dip Switch Settings .....                  | 6-32 |

| 6.6      | Specifications .....                              | 6-32 |

| 6.6.1    | RD50 Disk Drive Specifications .....              | 6-32 |

| 6.6.1.1  | Performance Specifications .....                  | 6-32 |

| 6.6.1.2  | Reliability Specifications .....                  | 6-32 |

|         |                                      |      |

|---------|--------------------------------------|------|

| 6.6.1.3 | Functional Specifications .....      | 6-33 |

| 6.6.1.4 | Electrical Specifications .....      | 6-33 |

| 6.6.1.5 | Environmental Specifications .....   | 6-33 |

| 6.6.2   | RD51 Disk Drive Specifications ..... | 6-34 |

| 6.6.2.1 | Performance Specifications .....     | 6-34 |

| 6.6.2.2 | Reliability Specifications .....     | 6-34 |

| 6.6.2.3 | Functional Specifications .....      | 6-34 |

| 6.6.2.4 | Electrical Specifications .....      | 6-35 |

| 6.6.2.5 | Environmental Specifications .....   | 6-35 |

## CHAPTER 7 RX50 CONTROLLER MODULE

|         |                                                       |      |

|---------|-------------------------------------------------------|------|

| 7.1     | General Information .....                             | 7-1  |

| 7.1.1   | Related Documentation .....                           | 7-1  |

| 7.1.2   | Controller Module .....                               | 7-2  |

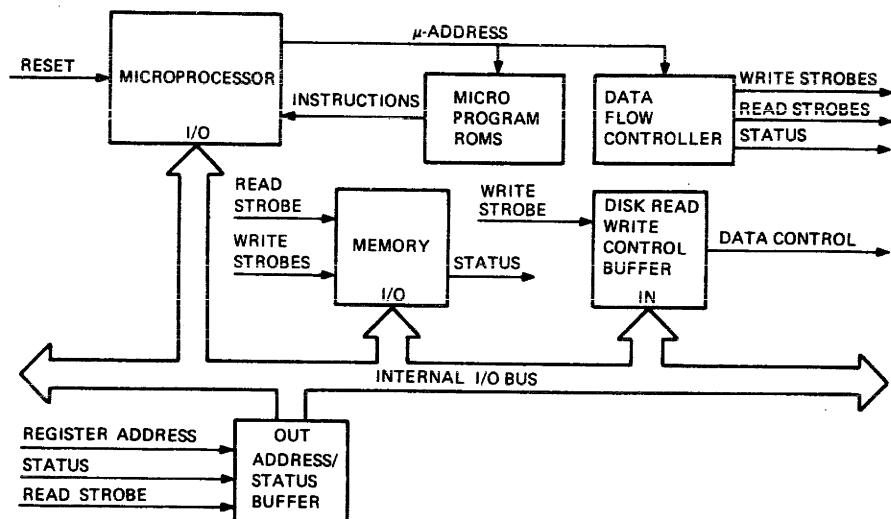

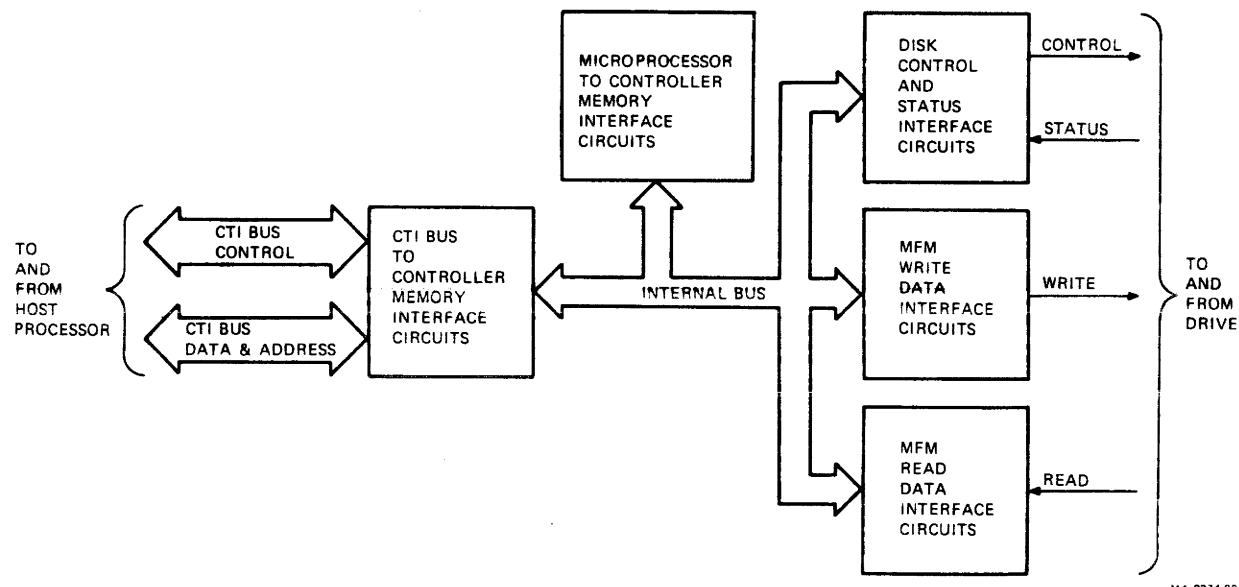

| 7.2     | Functional Components .....                           | 7-2  |

| 7.2.1   | Overview .....                                        | 7-2  |

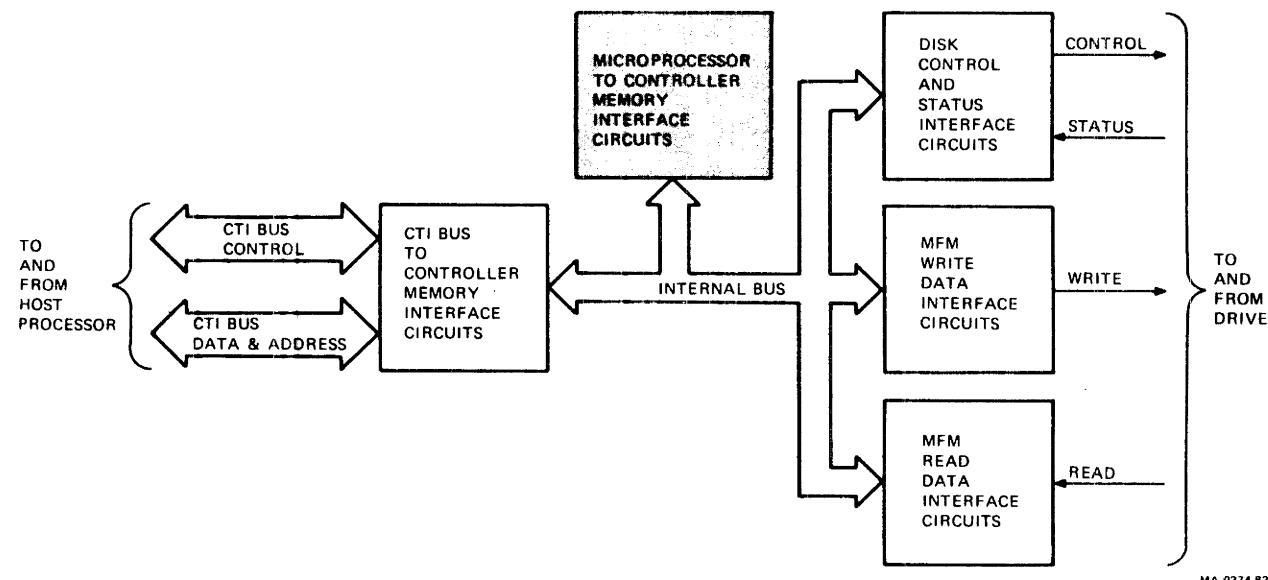

| 7.2.2   | CTI Bus to Controller Memory Interface .....          | 7-3  |

| 7.2.3   | Microprocessor to Controller Memory Interface .....   | 7-4  |

| 7.2.4   | Disk Control and Status Interface .....               | 7-4  |

| 7.2.5   | MFM Write Data Interface .....                        | 7-4  |

| 7.2.6   | MFM Read Data Interface .....                         | 7-4  |

| 7.3     | Theory of Operation .....                             | 7-5  |

| 7.3.1   | CTI Bus to Controller Memory Interface Detail .....   | 7-5  |

| 7.3.1.1 | RX50 Module Initialization .....                      | 7-5  |

| 7.3.1.2 | Interrupt Signal Generation .....                     | 7-8  |

| 7.3.1.3 | RX50 Module Acknowledgment .....                      | 7-8  |

| 7.3.1.4 | Host Processor to Controller Memory Accessing .....   | 7-8  |

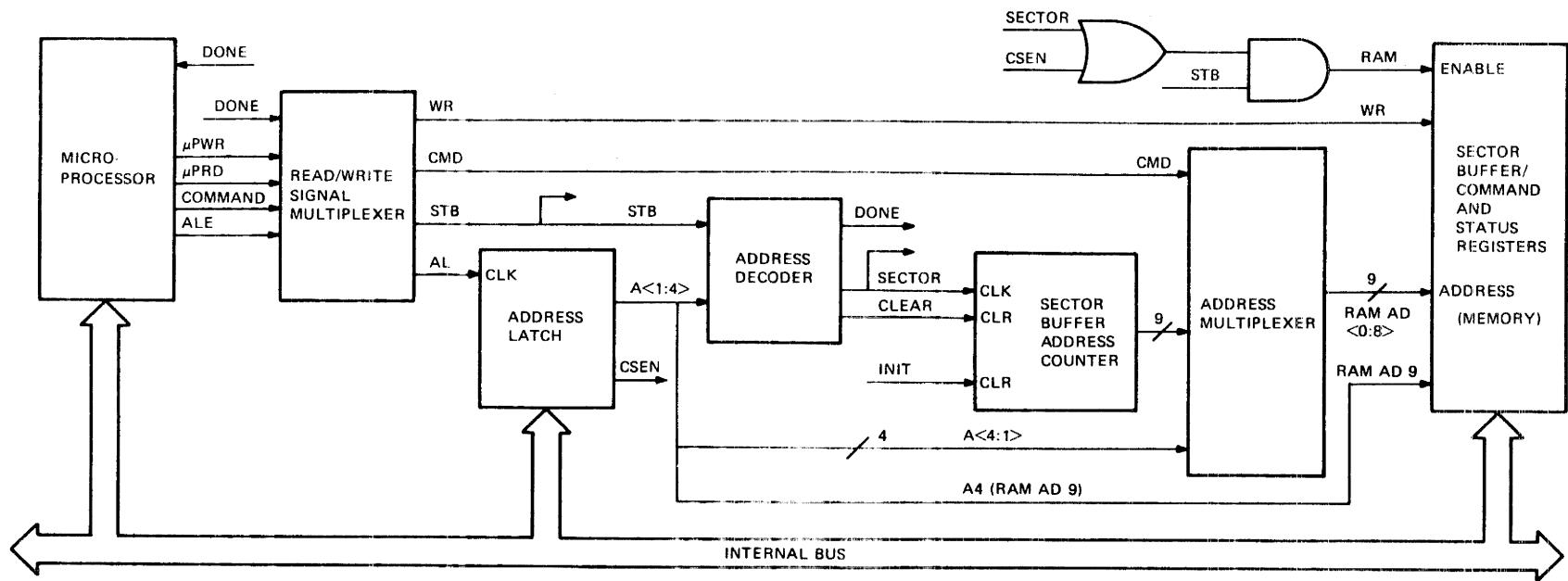

| 7.3.2   | Microprocessor to Controller Memory Accessing .....   | 7-10 |

| 7.3.2.1 | Command and Status Register Accessing .....           | 7-10 |

| 7.3.2.2 | Sector Buffer Memory Accessing .....                  | 7-12 |

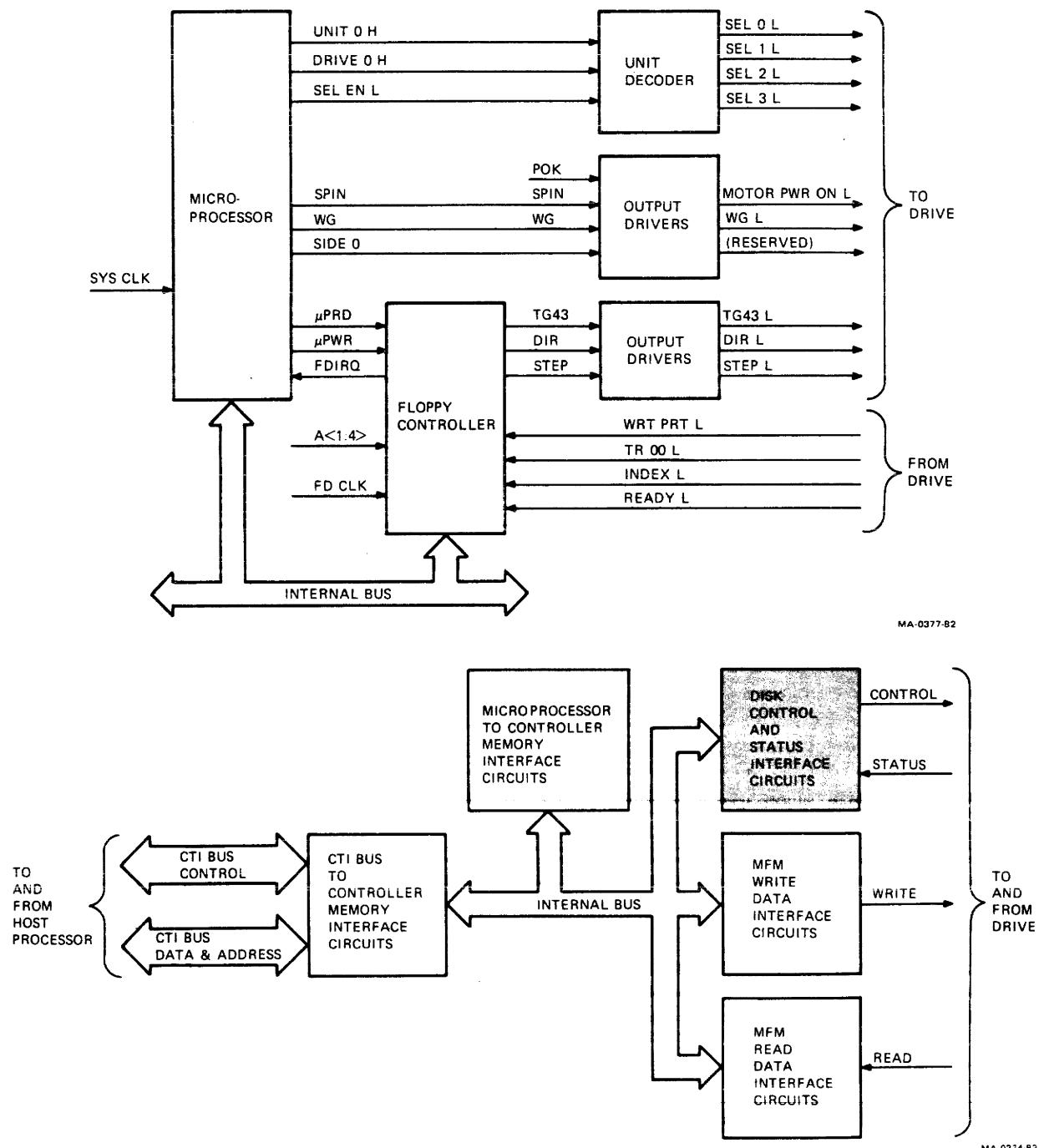

| 7.3.3   | Disk Control and Status Interface .....               | 7-13 |

| 7.3.3.1 | Control and Status Signal Processing .....            | 7-14 |

| 7.3.3.2 | Drive Select Signal Conversion .....                  | 7-14 |

| 7.3.3.3 | Drive Control Signal Gating .....                     | 7-14 |

| 7.3.4   | Write Data Interface Function .....                   | 7-15 |

| 7.3.4.1 | Write Data Bytes to Floppy Controller Transfers ..... | 7-15 |

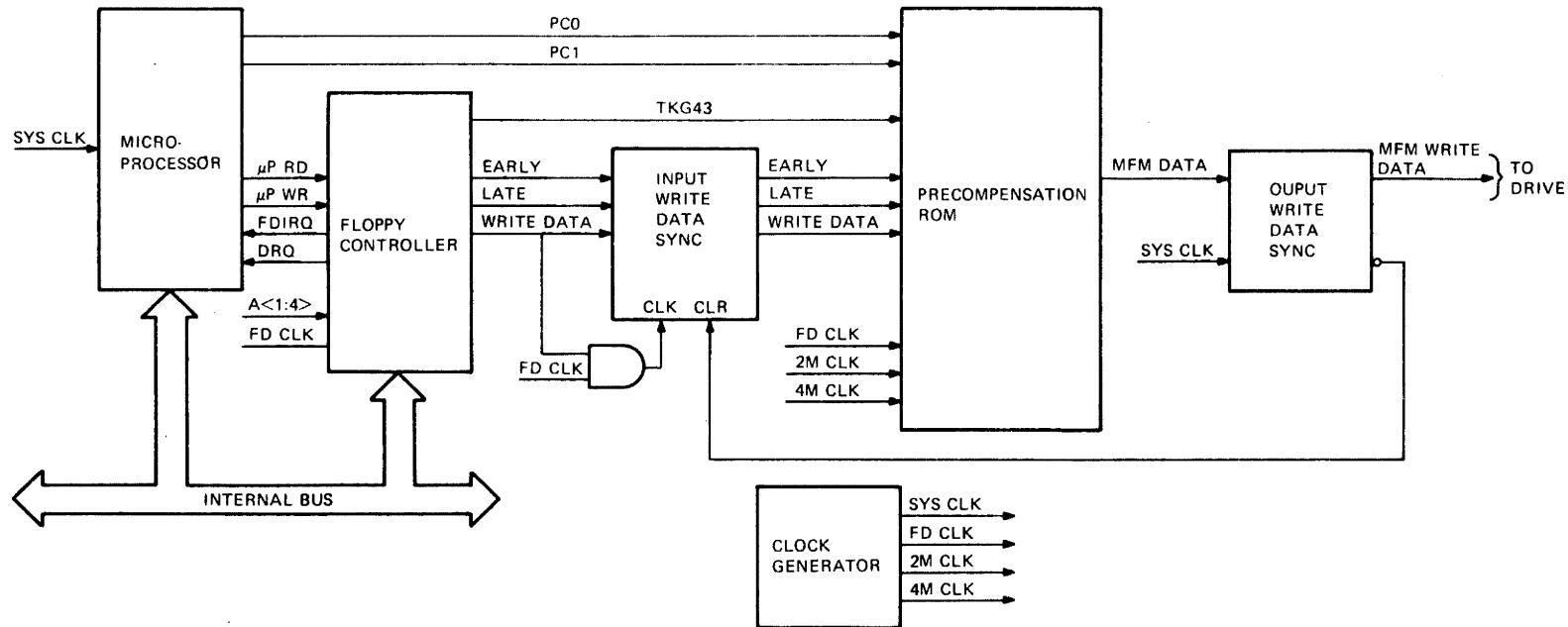

| 7.3.4.2 | MFM Encoding .....                                    | 7-17 |

| 7.3.4.3 | Write Data Precompensation .....                      | 7-17 |

| 7.3.4.4 | MFM Write Data Synchronization .....                  | 7-17 |

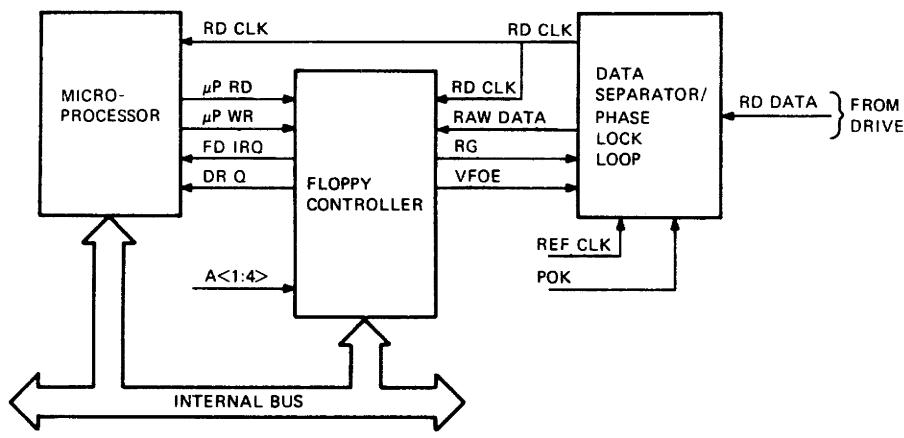

| 7.3.5   | MFM Read Data Interface .....                         | 7-18 |

| 7.3.5.1 | Data Separator and Phase-Locked Loop Operation .....  | 7-18 |

| 7.3.5.2 | Read Data Byte Conversion and Transfer .....          | 7-19 |

| 7.3.6   | Module Data Flow .....                                | 7-19 |

| 7.4     | Detailed Connector Descriptions .....                 | 7-20 |

| 7.4.1   | CTI Bus Interface J1 .....                            | 7-20 |

| 7.4.2   | Drive Interface Connector J2 .....                    | 7-22 |

| 7.4.2.1 | TKG43 L Output Signal .....                           | 7-23 |

| 7.4.2.2 | SEL 0 through SEL 3 Output Signals .....              | 7-23 |

|          |                                                           |      |

|----------|-----------------------------------------------------------|------|

| 7.4.2.3  | TK 00 L Input Signal .....                                | 7-23 |

| 7.4.2.4  | MOTOR PWR ON L Output Signal .....                        | 7-23 |

| 7.4.2.5  | DIR Output Signal .....                                   | 7-23 |

| 7.4.2.6  | STEP L Output Signal .....                                | 7-23 |

| 7.4.2.7  | WRT DATA L Output Signal .....                            | 7-23 |

| 7.4.2.8  | WG L Output Signal .....                                  | 7-23 |

| 7.4.2.9  | INDEX L Input Signal .....                                | 7-23 |

| 7.4.2.10 | WRT PRT L Input Signal .....                              | 7-23 |

| 7.4.2.11 | RD DATA L Input Signal .....                              | 7-23 |

| 7.4.2.12 | READY Input Signal .....                                  | 7-23 |

| 7.5      | Programming .....                                         | 7-24 |

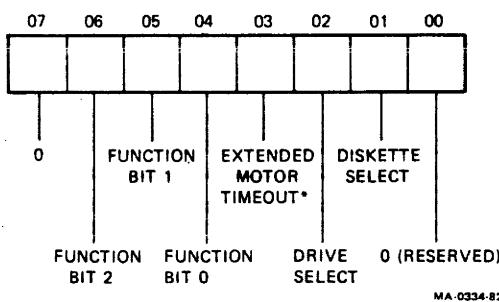

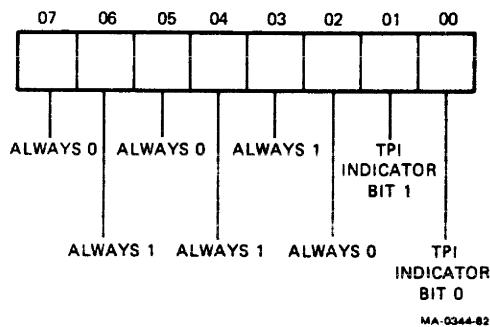

| 7.5.1    | RX51D Identification Register (X00) .....                 | 7-25 |

| 7.5.2    | RX5CS0 Register (X04) .....                               | 7-25 |

| 7.5.2.1  | Command Mode Bits .....                                   | 7-25 |

| 7.5.2.2  | Maintenance Status Mode .....                             | 7-27 |

| 7.5.2.3  | Read/Write Status Mode .....                              | 7-28 |

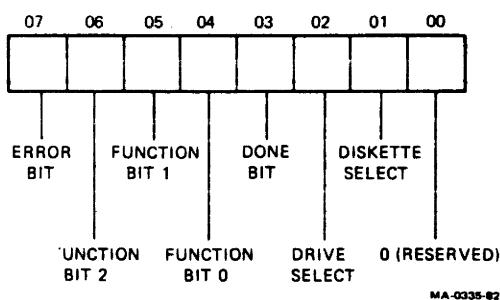

| 7.5.3    | RX5CS1 Register (X06) .....                               | 7-28 |

| 7.5.3.1  | Command Mode Bit .....                                    | 7-28 |

| 7.5.3.2  | Maintenance Status Mode .....                             | 7-28 |

| 7.5.3.3  | Read/Write Status Mode .....                              | 7-28 |

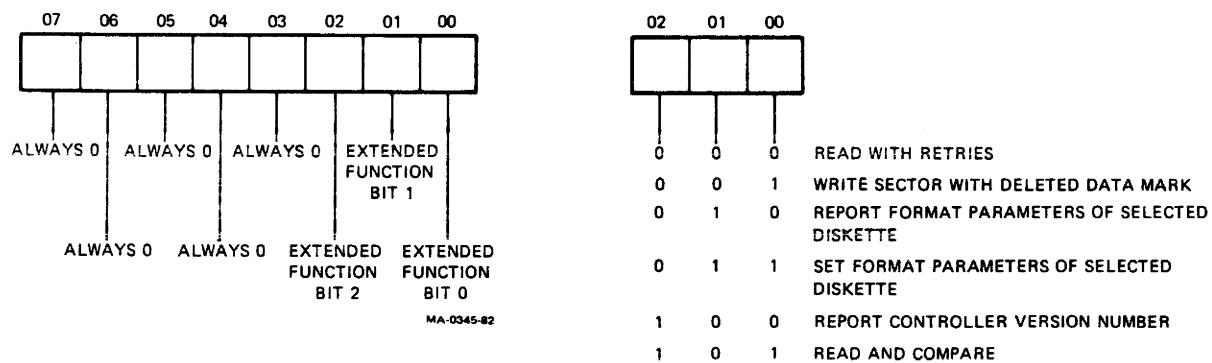

| 7.5.3.4  | Extended Functions Mode .....                             | 7-28 |

| 7.5.4    | RX5CS2 Register (X10) .....                               | 7-30 |

| 7.5.4.1  | Command Mode .....                                        | 7-30 |

| 7.5.4.2  | Maintenance Status Mode .....                             | 7-30 |

| 7.5.4.3  | Read/Write Status Mode .....                              | 7-30 |

| 7.5.4.4  | Extended Functions Mode .....                             | 7-31 |

| 7.5.5    | RX5CS3 Register (X12) .....                               | 7-31 |

| 7.5.5.1  | Maintenance Mode Status .....                             | 7-31 |

| 7.5.5.2  | Read/Write Status Mode .....                              | 7-33 |

| 7.5.5.3  | Extended Functions Mode .....                             | 7-33 |

| 7.5.6    | RX5CS4 Register (X14) .....                               | 7-34 |

| 7.5.6.1  | Maintenance Status Mode .....                             | 7-34 |

| 7.5.6.2  | Read/Write Status Mode .....                              | 7-34 |

| 7.5.6.3  | Extended Functions Mode .....                             | 7-35 |

| 7.5.7    | RX5CS5 Register (X16) .....                               | 7-35 |

| 7.5.7.1  | Read With Retries (000) .....                             | 7-36 |

| 7.5.7.2  | Write Sector With Deleted DATA MARK (001) .....           | 7-36 |

| 7.5.7.3  | Report Format Parameters of Selected Diskette (010) ..... | 7-36 |

| 7.5.7.4  | Set Format Parameters of Selected Diskette (011) .....    | 7-36 |

| 7.5.7.5  | Report Controller Version Number (100) .....              | 7-37 |

| 7.5.7.6  | Read and Compare (101) .....                              | 7-37 |

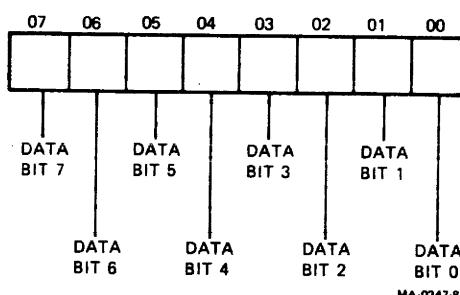

| 7.5.8    | RX5EB Empty Data Buffer (X20) .....                       | 7-37 |

| 7.5.9    | RX5CA Clear Address (X22) .....                           | 7-38 |

| 7.5.10   | RX5GO Start Command (X24) .....                           | 7-38 |

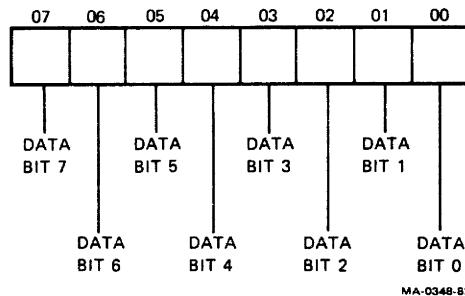

| 7.5.11   | RX5FB Fill Sector Buffer (X26) .....                      | 7-38 |

| 7.5.12   | Command and Status Register Summary .....                 | 7-38 |

| 7.6      | General Operating Sequence .....                          | 7-39 |

| 7.6.1    | Read/Write Operations .....                               | 7-40 |

| 7.6.1.1  | Read/Write Status .....                                   | 7-41 |

|         |                                                        |      |

|---------|--------------------------------------------------------|------|

| 7.6.2   | Maintenance Operations .....                           | 7-41 |

| 7.6.2.1 | Maintenance Status .....                               | 7-41 |

| 7.6.3   | Controller Initialization and Self-Test Sequence ..... | 7-41 |

| 7.7     | Specifications .....                                   | 7-43 |

| 7.7.1   | Electrical Specifications .....                        | 7-43 |

| 7.7.2   | Environmental Specifications .....                     | 7-43 |

| 7.7.3   | Physical Specifications .....                          | 7-43 |

## CHAPTER 8 RX50 DUAL DISKETTE DRIVE

|         |                                                       |      |

|---------|-------------------------------------------------------|------|

| 8.1     | General Information .....                             | 8-1  |

| 8.1.1   | Related Documentation .....                           | 8-1  |

| 8.1.2   | RX50 Dual Diskette Drive .....                        | 8-1  |

| 8.1.3   | Physical Description .....                            | 8-2  |

| 8.1.4   | Diskette Description .....                            | 8-2  |

| 8.1.4.1 | Diskette Handling and Storage .....                   | 8-3  |

| 8.1.4.2 | Write Protection of Diskettes .....                   | 8-4  |

| 8.1.4.3 | Diskette Loading/Unloading .....                      | 8-4  |

| 8.1.5   | Configuration Options .....                           | 8-4  |

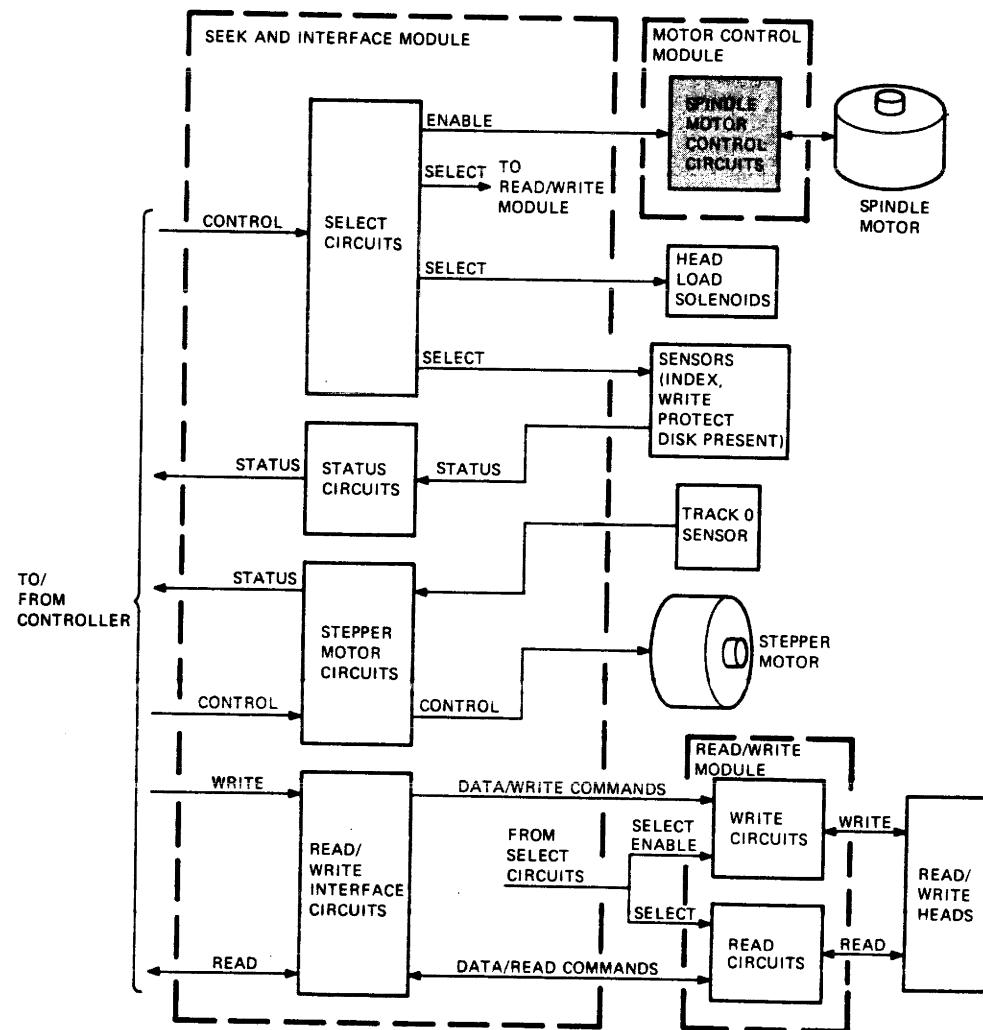

| 8.2     | Functional Components .....                           | 8-6  |

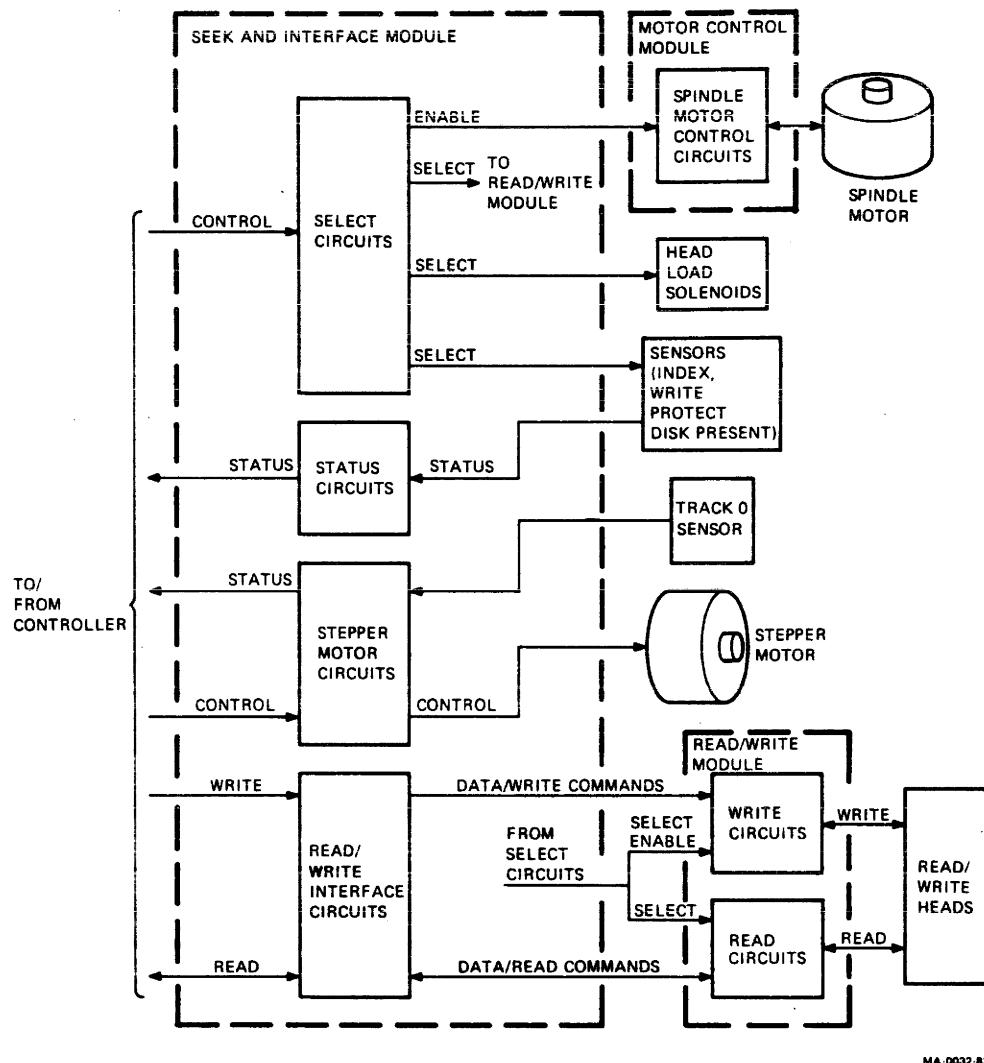

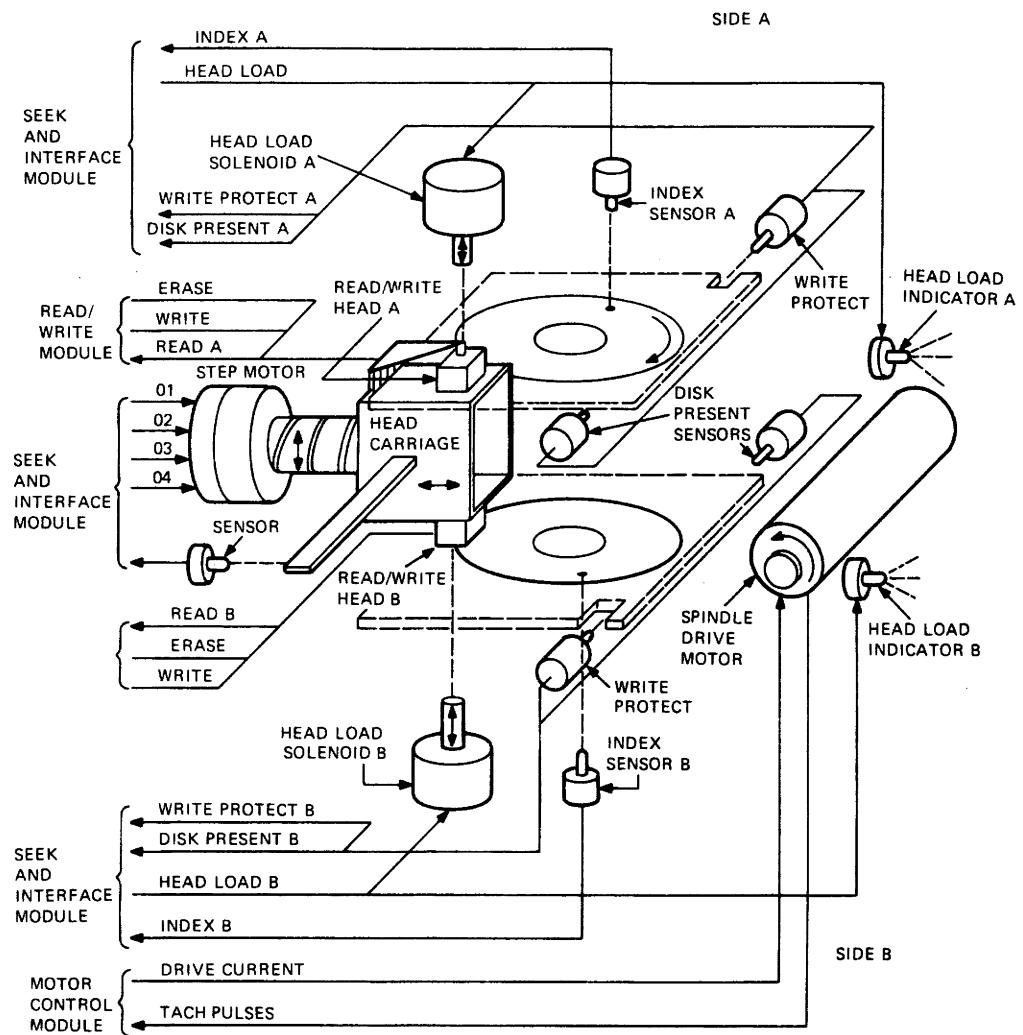

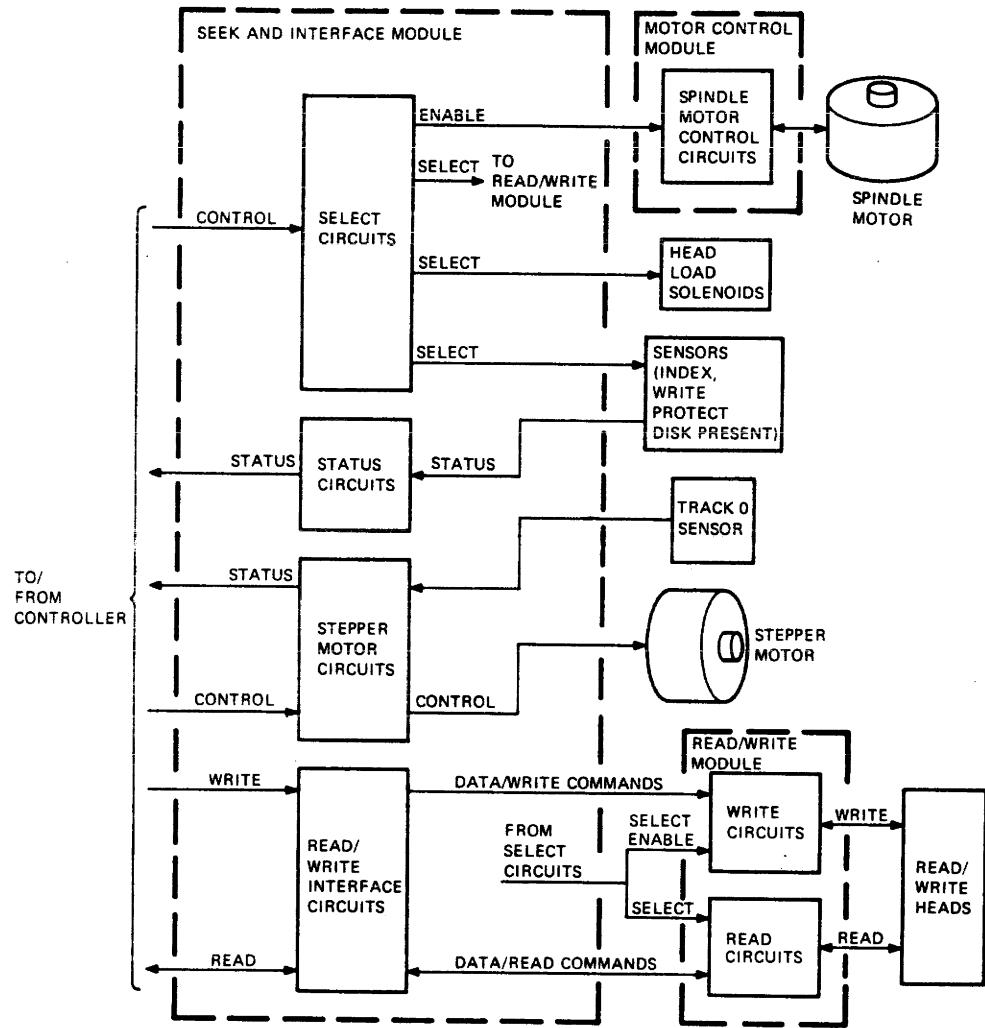

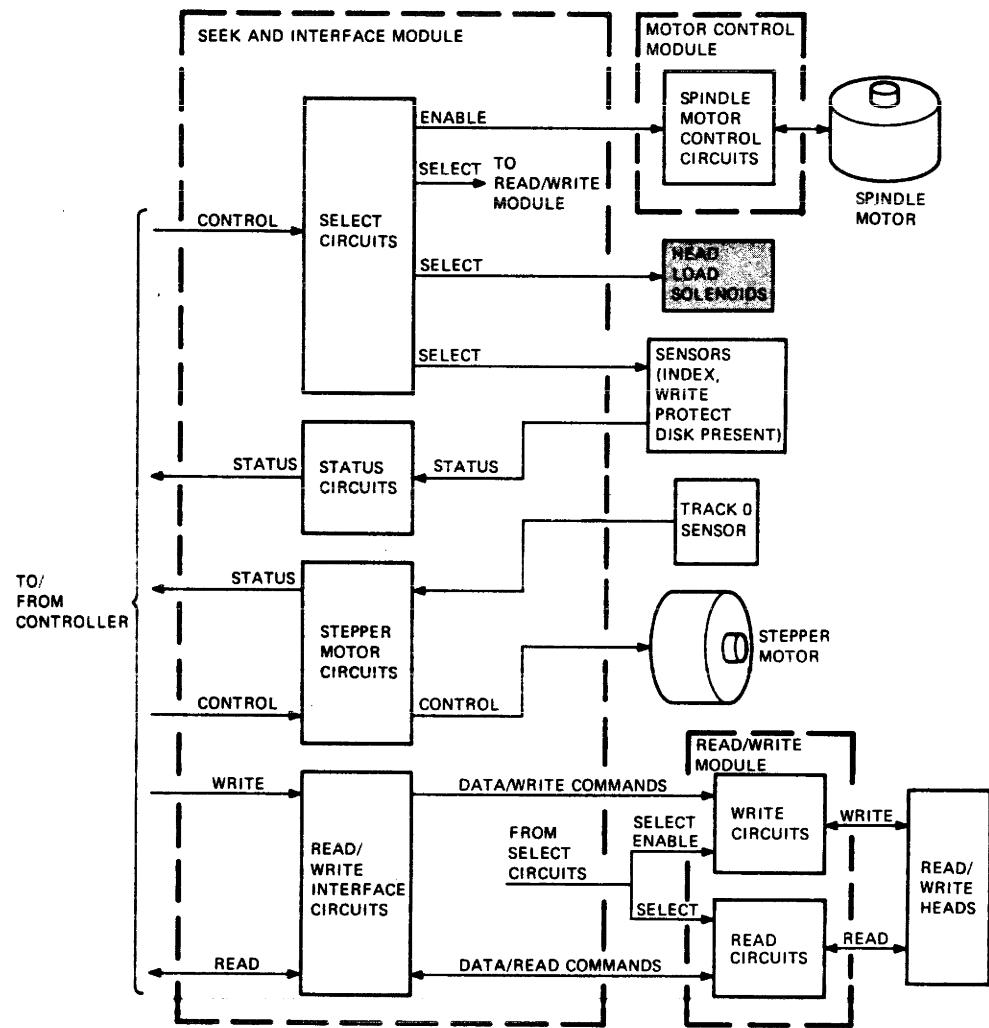

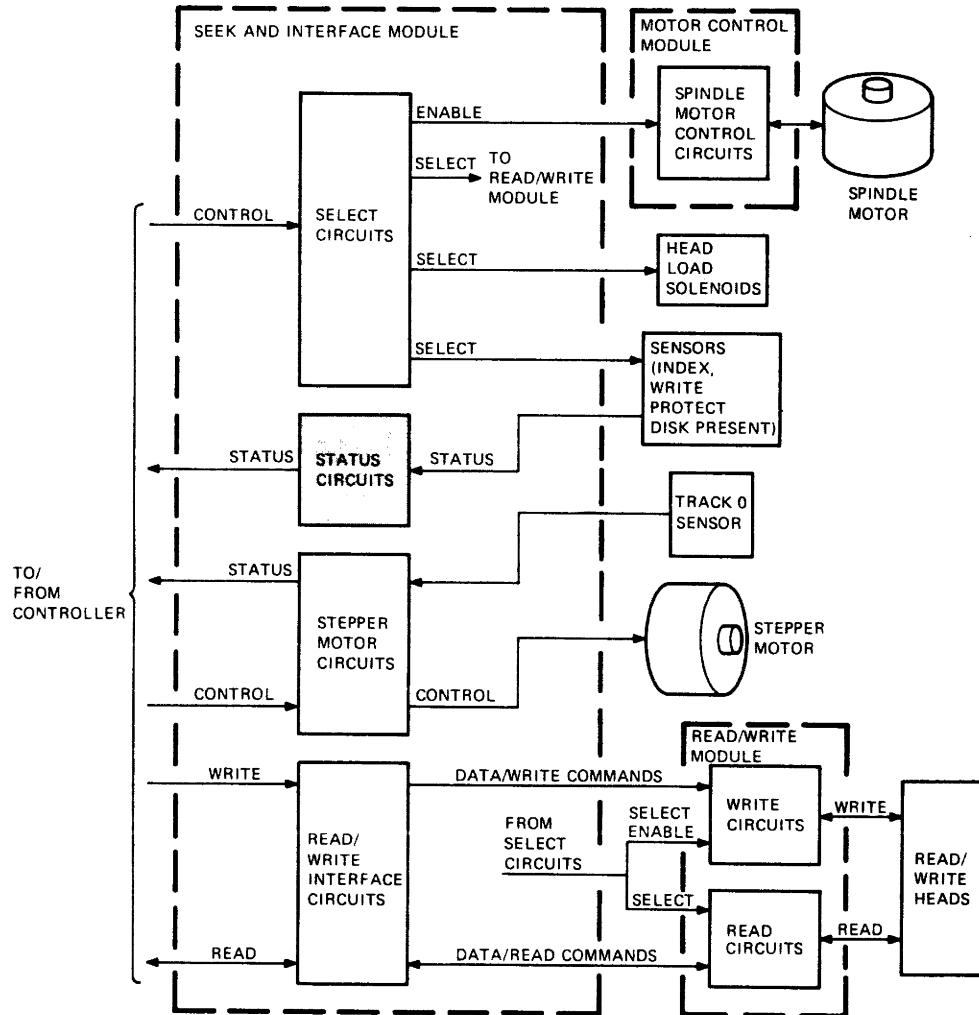

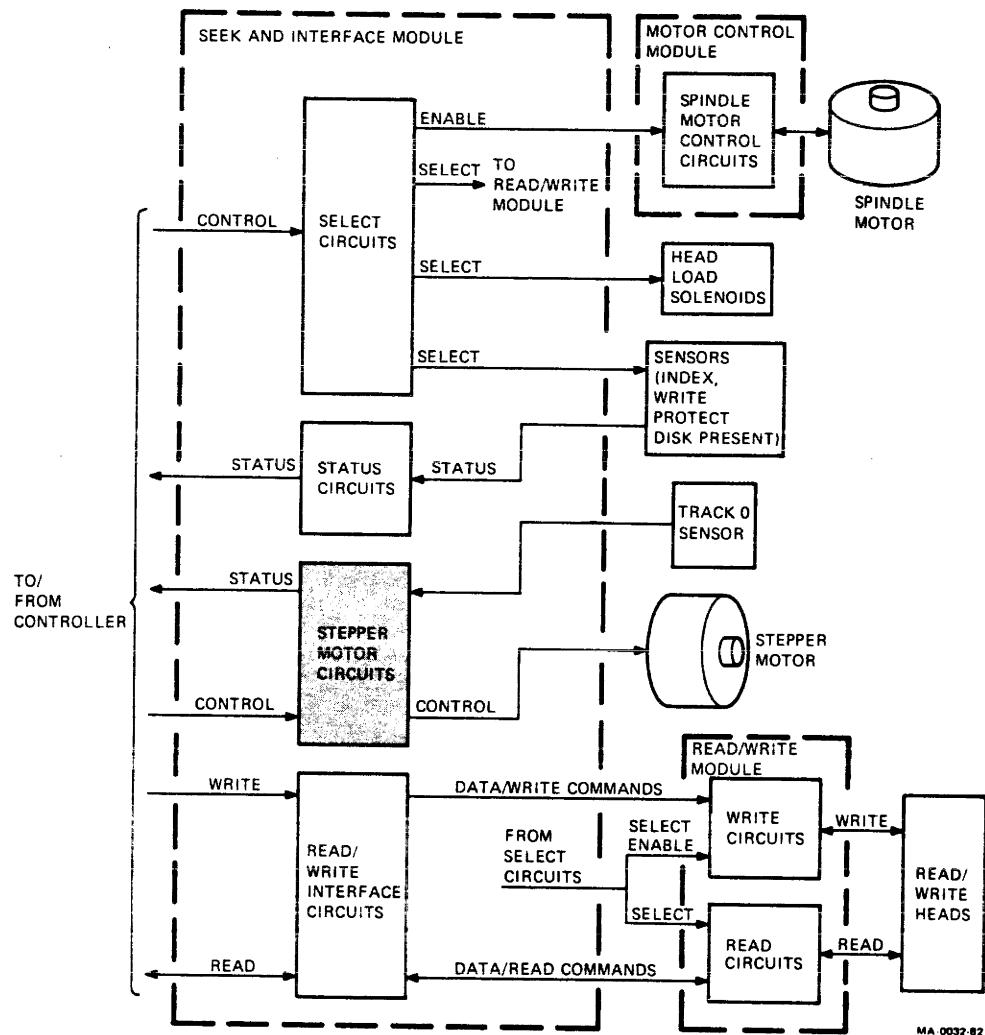

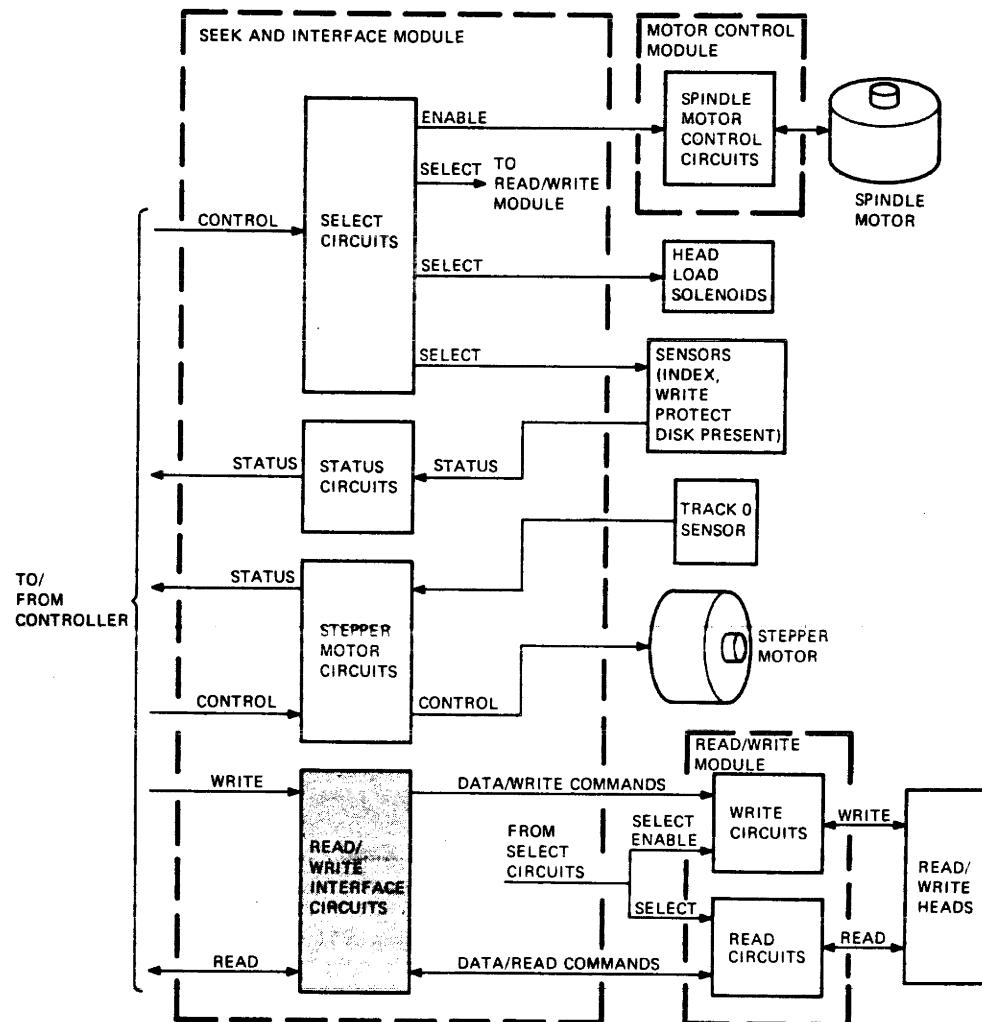

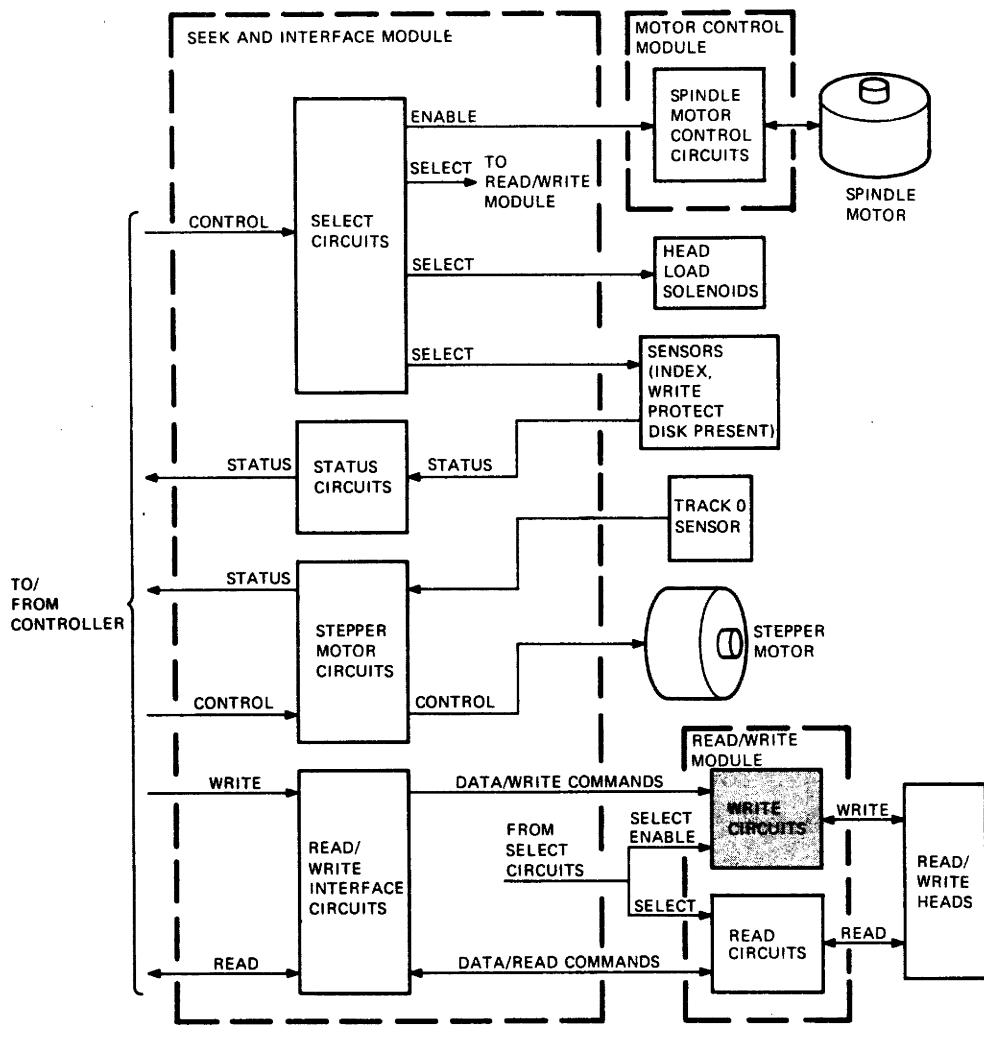

| 8.2.1   | Seek and Interface Module Functions .....             | 8-6  |

| 8.2.2   | Motor Control Module and Spindle Motor Function ..... | 8-7  |

| 8.2.3   | Head Load Solenoid Function .....                     | 8-8  |

| 8.2.4   | Sensor Functions .....                                | 8-8  |

| 8.2.5   | Stepper Motor Function .....                          | 8-8  |

| 8.2.6   | Read/Write Module Function .....                      | 8-8  |

| 8.2.7   | RX50 Drive Set-up Sequence .....                      | 8-8  |

| 8.3     | Theory of Operation .....                             | 8-8  |

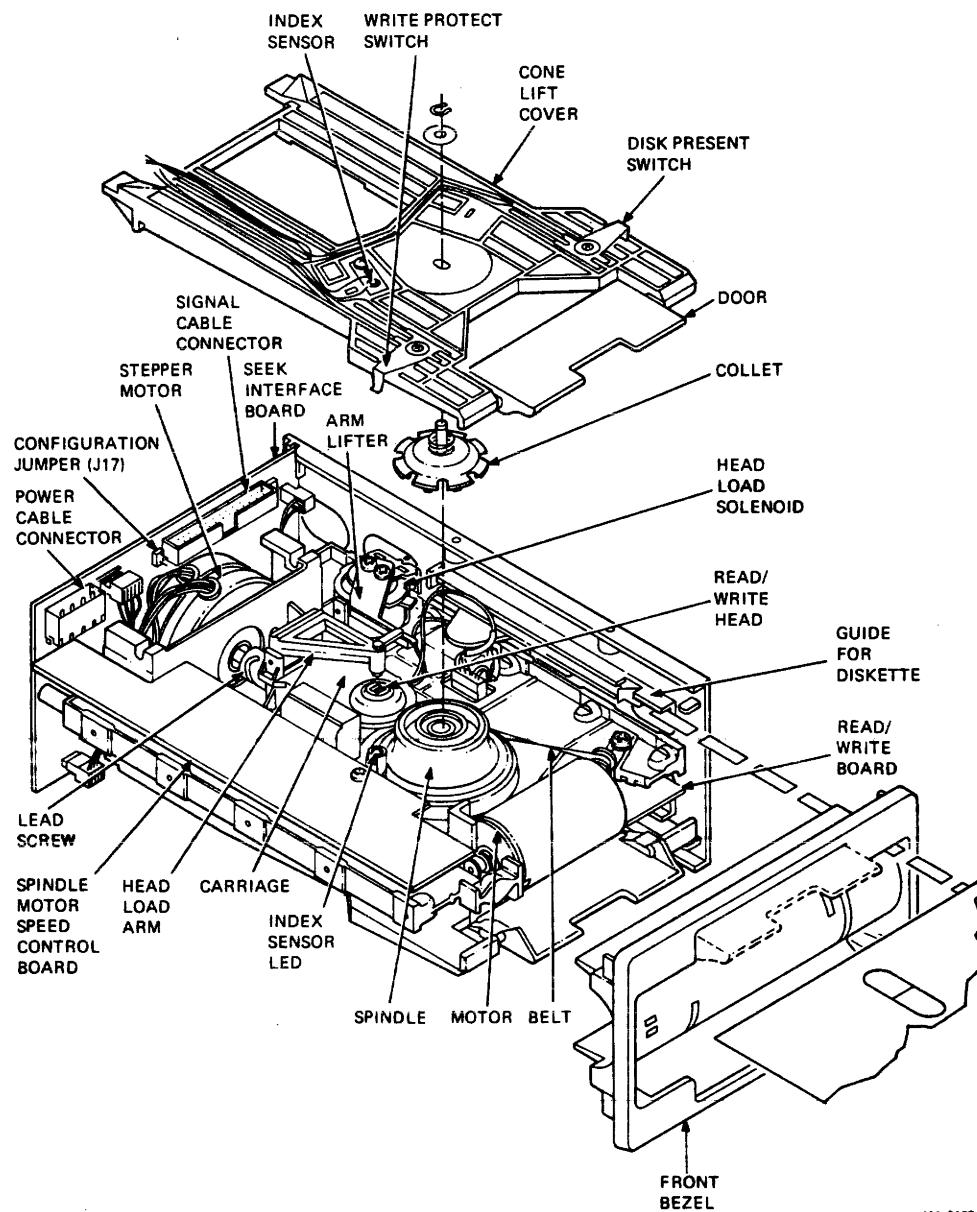

| 8.3.1   | Drive Mechanism .....                                 | 8-9  |

| 8.3.1.1 | Diskette Positioning Mechanism .....                  | 8-12 |

| 8.3.1.2 | Spindle Drive Mechanism .....                         | 8-12 |

| 8.3.1.3 | Head Positioning Mechanism .....                      | 8-12 |

| 8.3.1.4 | Head Load Mechanism .....                             | 8-13 |

| 8.3.1.5 | Sensors .....                                         | 8-13 |

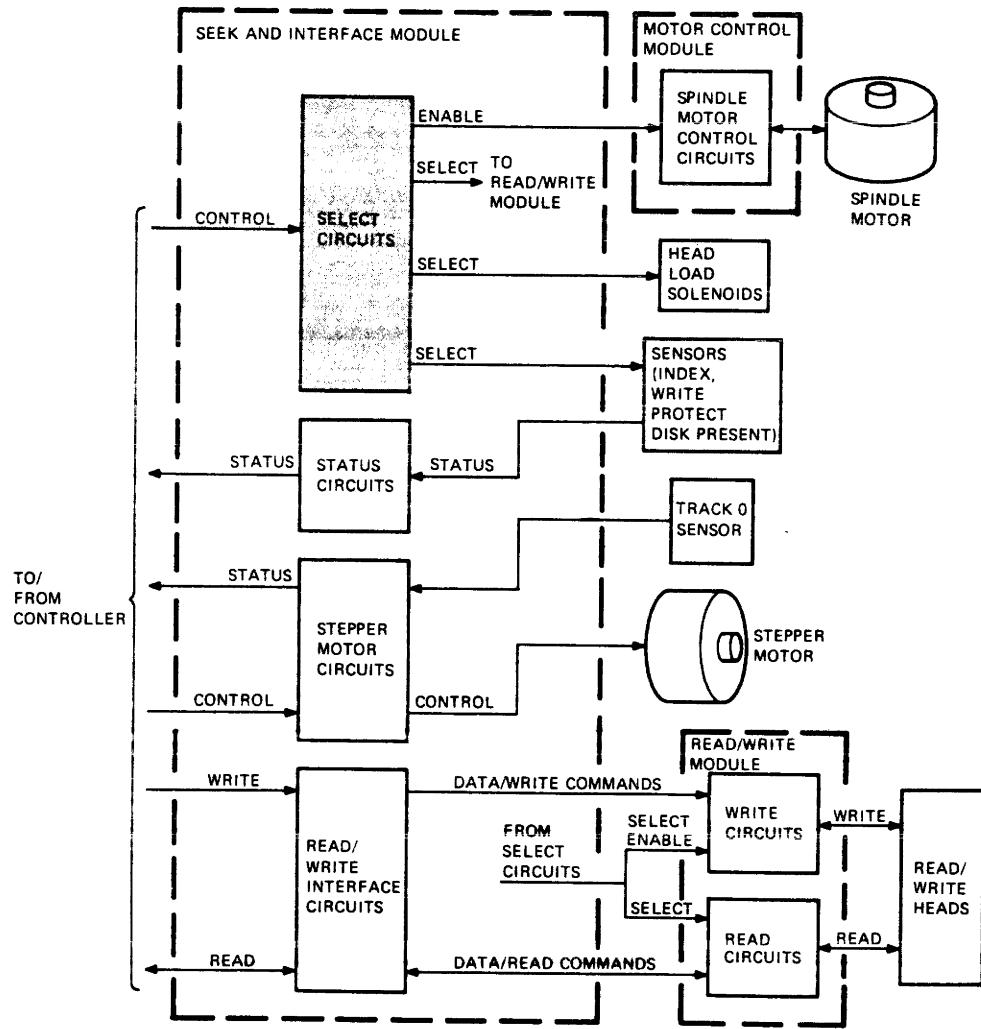

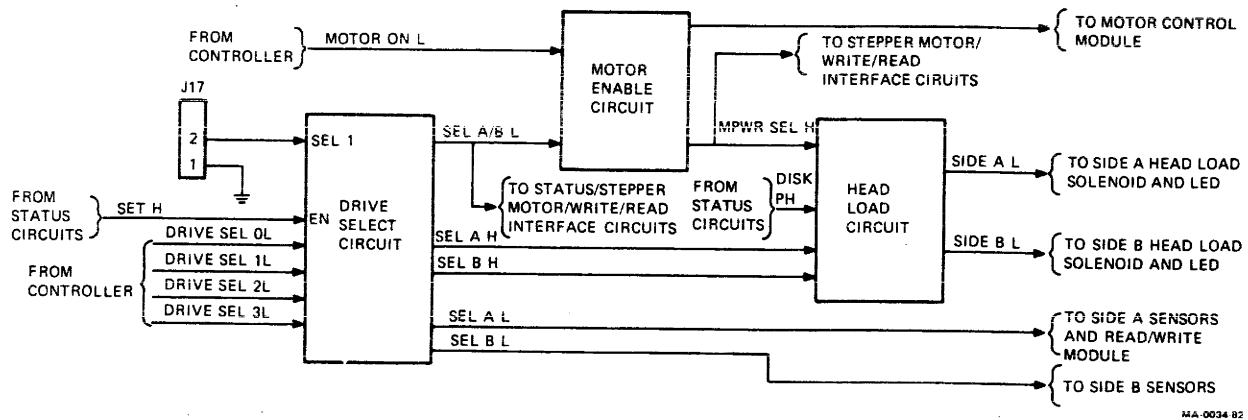

| 8.3.2   | Select Circuit Detailed Operation .....               | 8-14 |

| 8.3.2.1 | Drive Select Circuit .....                            | 8-14 |

| 8.3.2.2 | Motor Enable Circuit .....                            | 8-16 |

| 8.3.2.3 | Head Load Circuit .....                               | 8-16 |

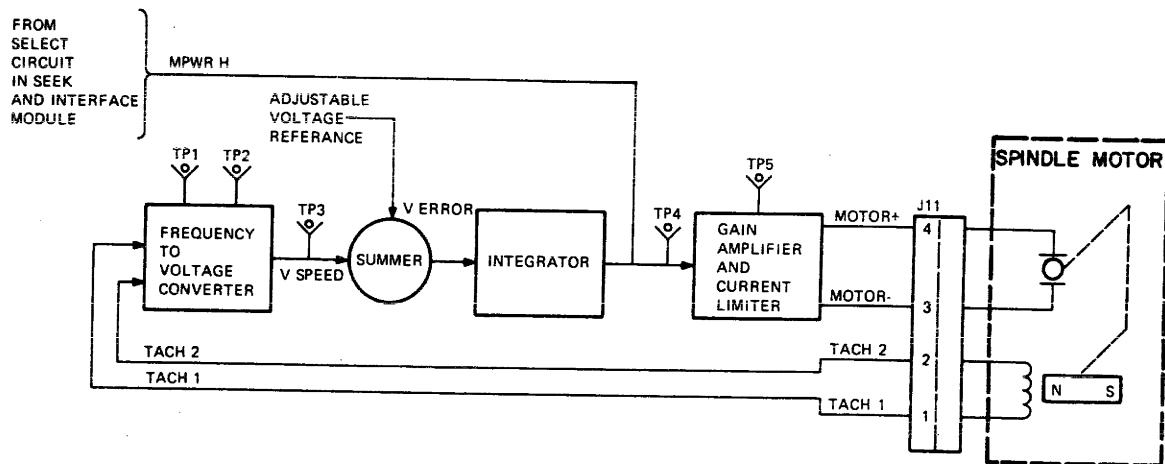

| 8.3.3   | Motor Control Circuit .....                           | 8-16 |

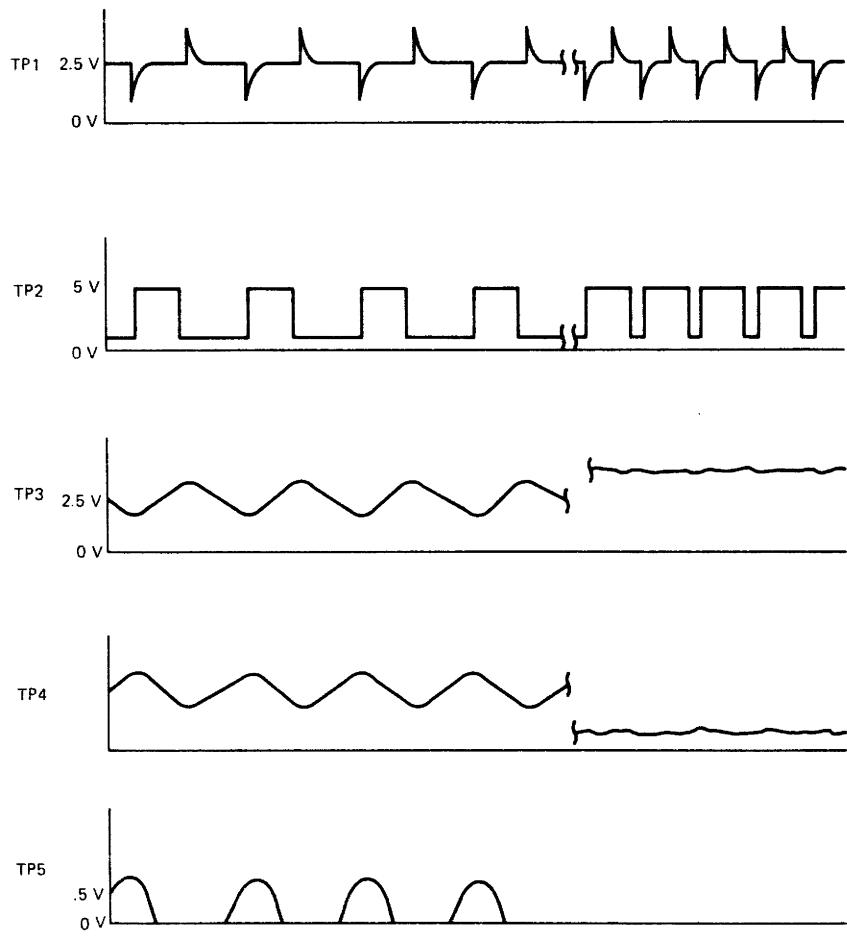

| 8.3.3.1 | Frequency to Voltage Converter .....                  | 8-18 |

| 8.3.3.2 | Summer .....                                          | 8-19 |

| 8.3.3.3 | Integrator .....                                      | 8-19 |

| 8.3.3.4 | Gain Amplifier and Current Limiter .....              | 8-19 |

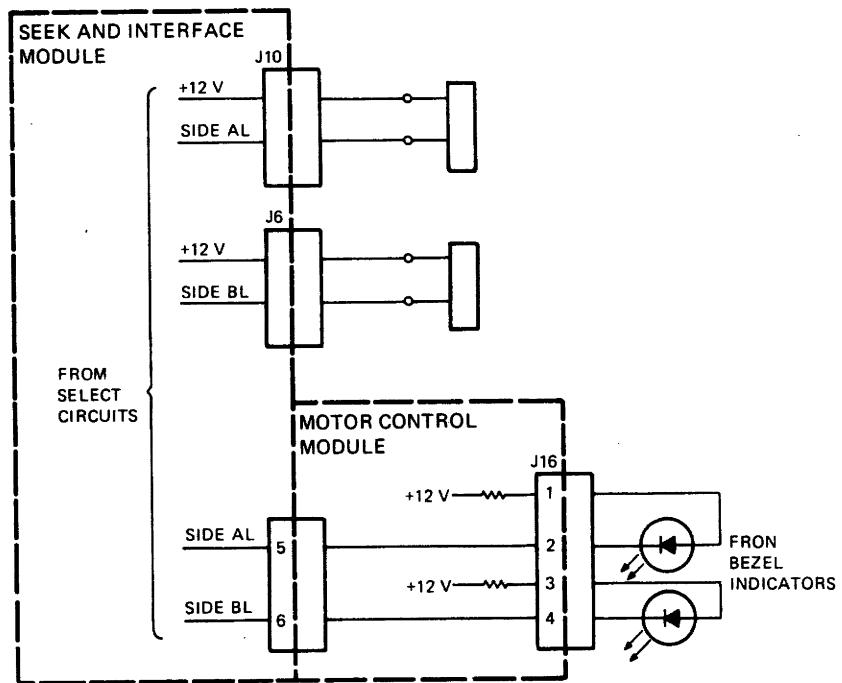

| 8.3.4   | Head Load Solenoids and Indicators .....              | 8-19 |

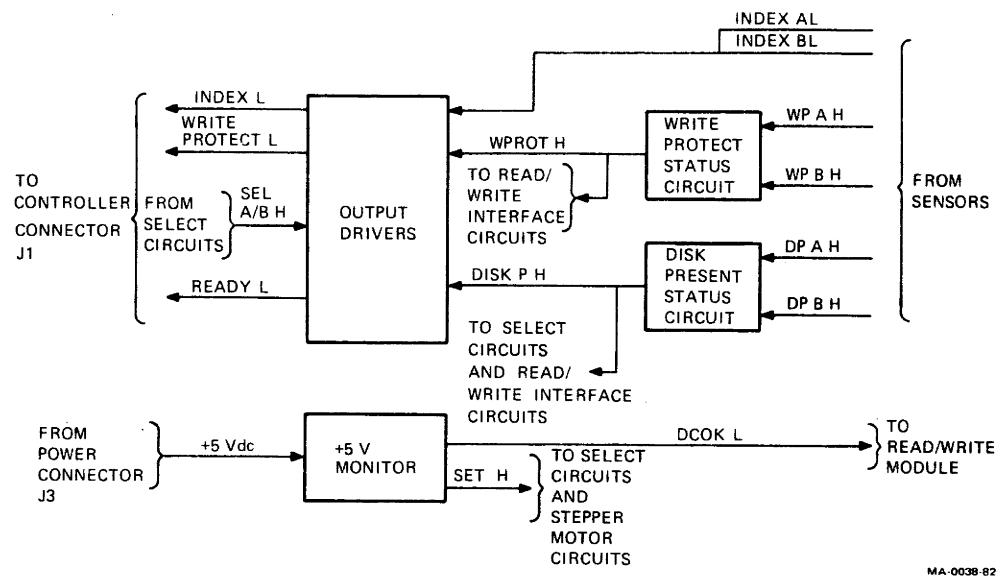

| 8.3.5   | Status Circuit .....                                  | 8-19 |

| 8.3.5.1 | Write Protect Status Circuit .....                    | 8-23 |

| 8.3.5.2 | Diskette Present Status Circuits .....                | 8-23 |

| 8.3.5.3 | Output Driver .....                                   | 8-23 |

| 8.3.5.4 | +5 V Monitor .....                                    | 8-23 |

|          |                                                             |      |

|----------|-------------------------------------------------------------|------|

| 8.3.6    | Status Sensors .....                                        | 8-24 |

| 8.3.6.1  | Index Sensor .....                                          | 8-24 |

| 8.3.6.2  | Diskette Present and Write Protect Sensor .....             | 8-25 |

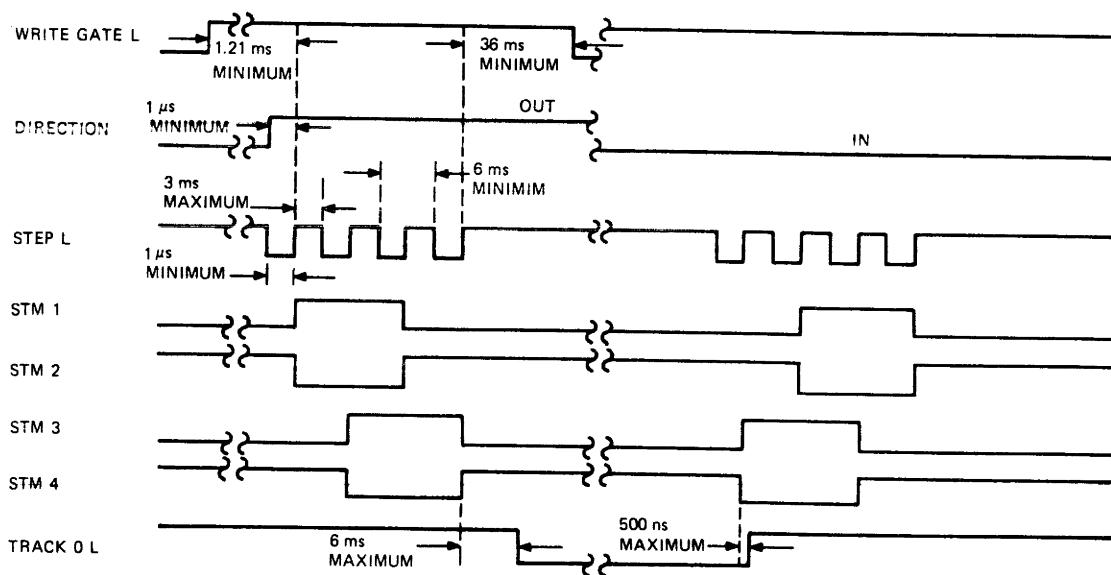

| 8.3.7    | Stepper Motor Circuits .....                                | 8-26 |

| 8.3.7.1  | Stepper Motor Driver .....                                  | 8-26 |

| 8.3.7.2  | Track 0 Sensor .....                                        | 8-28 |

| 8.3.7.3  | Track 0 Status Circuit .....                                | 8-28 |

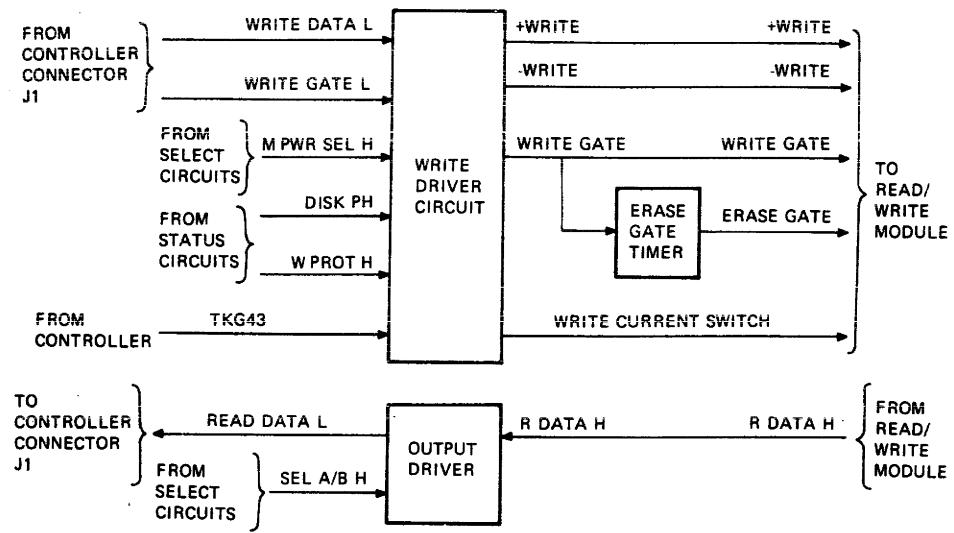

| 8.3.8    | Read/Write Interface Circuit .....                          | 8-28 |

| 8.3.8.1  | Write Driver Circuit .....                                  | 8-28 |

| 8.3.8.2  | Erase Gate Timer .....                                      | 8-31 |

| 8.3.8.3  | Output Driver .....                                         | 8-31 |

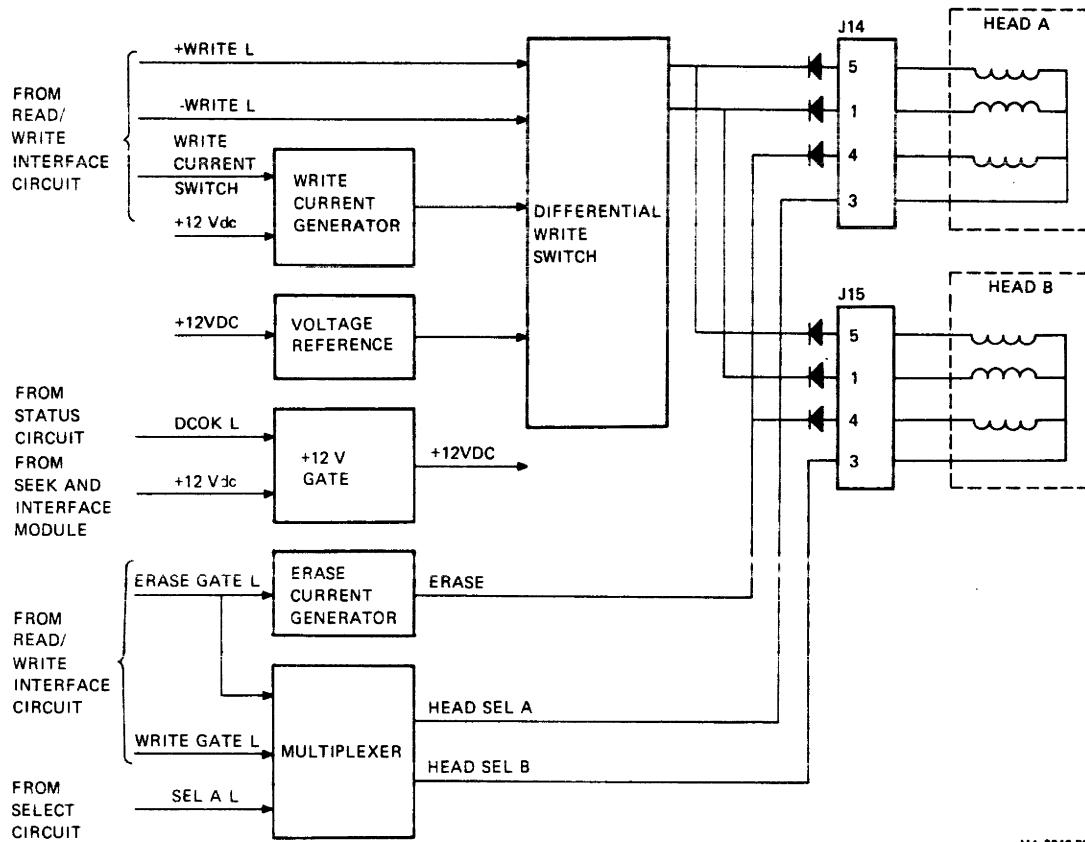

| 8.3.9    | Write Circuit .....                                         | 8-31 |

| 8.3.9.1  | Write Current Generator .....                               | 8-33 |

| 8.3.9.2  | Voltage Reference .....                                     | 8-33 |

| 8.3.9.3  | +12 V Gate .....                                            | 8-33 |

| 8.3.9.4  | Differential Write Switch .....                             | 8-33 |

| 8.3.9.5  | Erase Gate Generator .....                                  | 8-33 |

| 8.3.9.6  | Multiplexer .....                                           | 8-34 |

| 8.3.10   | Read Circuit .....                                          | 8-34 |

| 8.3.10.1 | Read Amplifier .....                                        | 8-36 |

| 8.3.10.2 | Multiplexer .....                                           | 8-36 |

| 8.3.11   | Write/Read Head .....                                       | 8-37 |

| 8.4      | Intermodule Signal Definitions .....                        | 8-37 |

| 8.4.1    | Seek and Interface/Controller Module Connector J1 .....     | 8-37 |

| 8.4.1.1  | TKG43 L Input Signal .....                                  | 8-39 |

| 8.4.1.2  | DRIVE SEL 0 thru DRIVE SEL 3 Input Signals .....            | 8-39 |

| 8.4.1.3  | TRACK 0 L Output Signal .....                               | 8-39 |

| 8.4.1.4  | MOTOR ON L Input Signal .....                               | 8-39 |

| 8.4.1.5  | DIRECTION Input Signal .....                                | 8-39 |

| 8.4.1.6  | STEP L Input Signal .....                                   | 8-39 |

| 8.4.1.7  | WRITE DATA L Input Signal .....                             | 8-39 |

| 8.4.1.8  | WRITE GATE L Input Signal .....                             | 8-39 |

| 8.4.1.9  | INDEX L Output Signal .....                                 | 8-40 |

| 8.4.1.10 | WRITE PROTECT L Output Signal .....                         | 8-40 |

| 8.4.1.11 | READ DATA L Output Signal .....                             | 8-40 |

| 8.4.1.12 | READY Output Signal .....                                   | 8-40 |

| 8.4.2    | Seek and Interface/Motor Control Modules Connector J4 ..... | 8-40 |

| 8.4.2.1  | MPWR H Input Signal .....                                   | 8-40 |

| 8.4.2.2  | SIDE A L Input Signal .....                                 | 8-40 |

| 8.4.2.3  | SIDE B L Input Signal .....                                 | 8-40 |

| 8.4.3    | Seek and Interface/Read Write Modules Connector J9 .....    | 8-41 |

| 8.4.3.1  | DCOK L Output Signal .....                                  | 8-41 |

| 8.4.3.2  | ±WRITE L Output Signals .....                               | 8-41 |

| 8.4.3.3  | R DATA H Input Signals .....                                | 8-41 |

| 8.4.3.4  | W GATE L Output Signal .....                                | 8-41 |

| 8.4.3.5  | WRITE CURRENT SWITCH Output Signal .....                    | 8-41 |

| 8.4.3.6  | ERASE GATE L Output Signal .....                            | 8-41 |

| 8.4.3.7  | SEL A L Output Signal .....                                 | 8-41 |

| 8.4.4    | Seek and Interface Power Connector J3 .....                 | 8-42 |

|         |                                                                      |      |

|---------|----------------------------------------------------------------------|------|

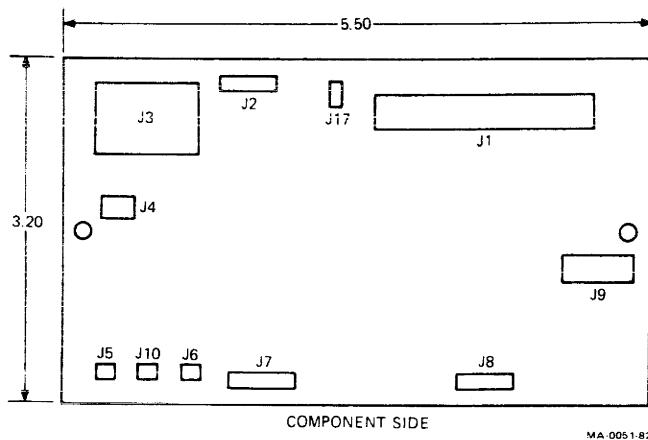

| 8.4.5   | Seek and Interface Connectors J2, J5, J6, J7, J8, J10, and J17 ..... | 8-42 |

| 8.4.5.1 | Side A Switches and Indicators Connector J2 .....                    | 8-42 |

| 8.4.5.2 | Track 0 Sensor Connector J5 .....                                    | 8-42 |

| 8.4.5.3 | Side B Head Load Solenoid Connector J6 .....                         | 8-42 |

| 8.4.5.4 | Stepper Motor Connector J7 .....                                     | 8-42 |

| 8.4.5.5 | Side B Switches and Indicators Connector J8 .....                    | 8-43 |

| 8.4.5.6 | Side A Head Load Solenoid Connector J10 .....                        | 8-43 |

| 8.4.5.7 | Drive Select Jumper J17 .....                                        | 8-43 |

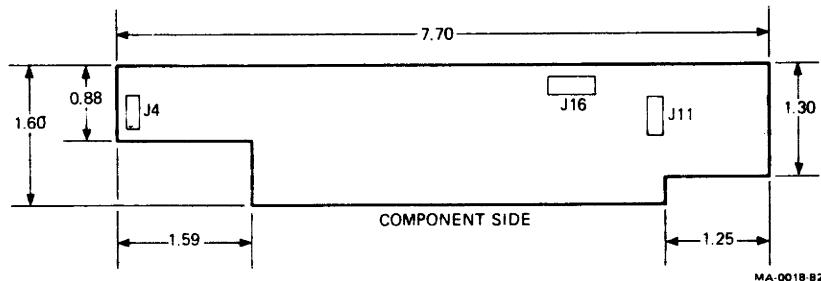

| 8.4.6   | Motor Control Modules Connectors J4, J11, J16 .....                  | 8-43 |

| 8.4.6.1 | Spindle Motor Connector J11 .....                                    | 8-43 |

| 8.4.6.2 | Front Panel Operational Indicators Connector J16 .....               | 8-44 |

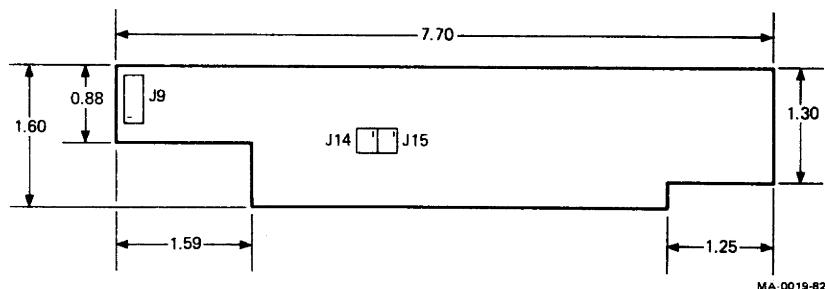

| 8.4.7   | Read/Write Module Connectors J9, J14, J15 .....                      | 8-44 |

| 8.4.7.1 | Side A Read, Write, and Erase Head Connector J14 .....               | 8-44 |

| 8.4.7.2 | Side B Read, Write, and Erase Head Connector J15 .....               | 8-44 |

| 8.5     | Specifications .....                                                 | 8-45 |

| 8.5.1   | Performance Specifications .....                                     | 8-45 |

| 8.5.2   | Reliability Specifications .....                                     | 8-45 |

| 8.5.3   | Functional Specifications .....                                      | 8-46 |

| 8.5.4   | Electrical Specifications .....                                      | 8-46 |

| 8.5.5   | Environmental Specifications .....                                   | 8-46 |

| 8.5.6   | Mechanical Specifications .....                                      | 8-46 |

## CHAPTER 9 RD52-A DISK DRIVE

|         |                                               |      |

|---------|-----------------------------------------------|------|

| 9.1     | Introduction .....                            | 9-1  |

| 9.2     | Product Description .....                     | 9-1  |

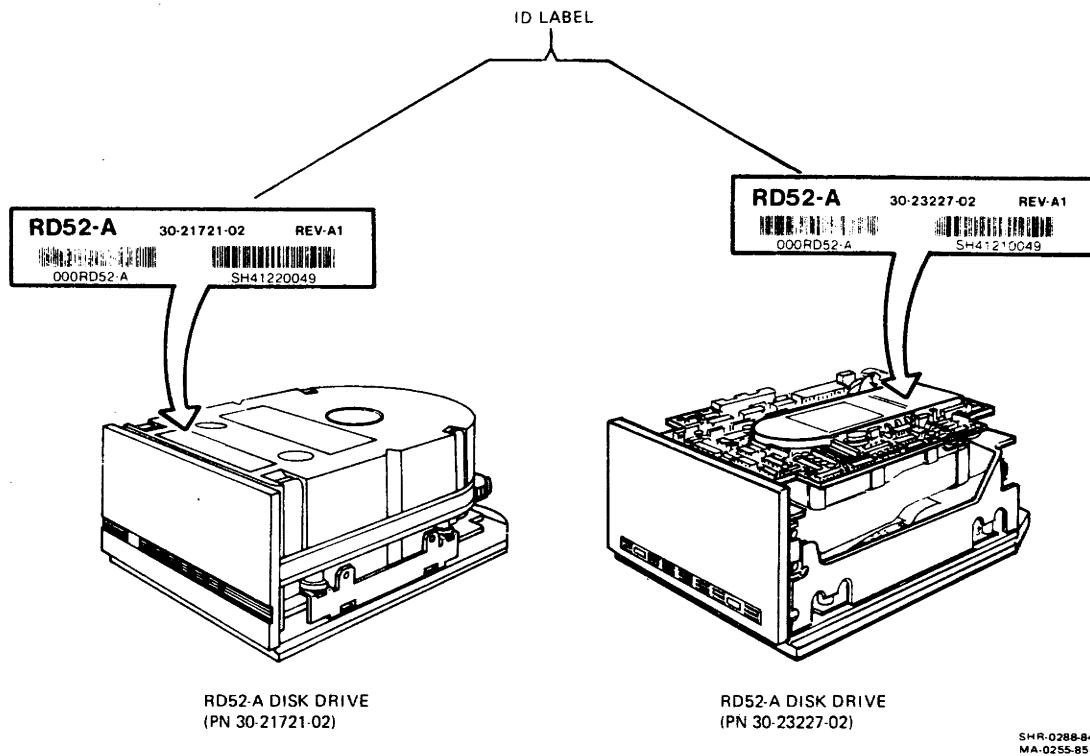

| 9.3     | Identifying Your RD52-A Disk Drive .....      | 9-1  |

| 9.4     | RD52-A General Specifications .....           | 9-3  |

| 9.5     | Related Documentation .....                   | 9-3  |

| 9.6     | RD52-A (30-21721-01) Disk Drive .....         | 9-4  |

| 9.6.1   | General .....                                 | 9-5  |

| 9.6.2   | Specifications .....                          | 9-5  |

| 9.6.2.1 | Physical Specifications .....                 | 9-5  |

| 9.6.2.2 | Performance Specifications .....              | 9-6  |

| 9.6.2.3 | Functional Specifications .....               | 9-6  |

| 9.6.3   | Power Requirements .....                      | 9-6  |

| 9.6.3.1 | DC Power .....                                | 9-6  |

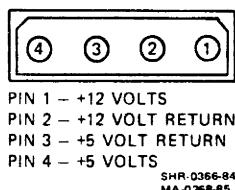

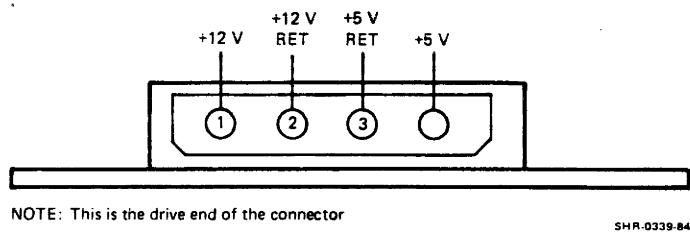

| 9.6.3.2 | DC Power Connector .....                      | 9-6  |

| 9.7     | Physical Description .....                    | 9-8  |

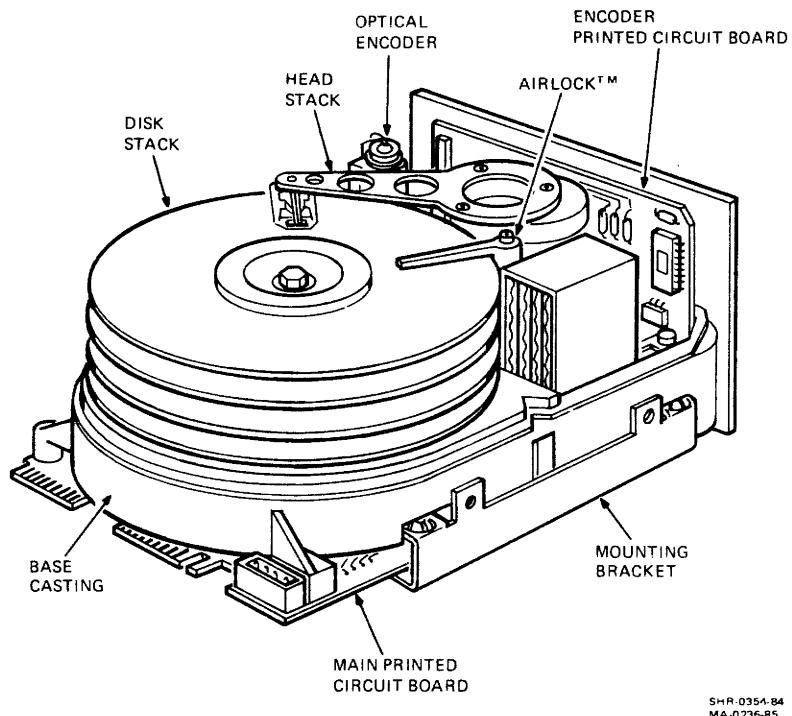

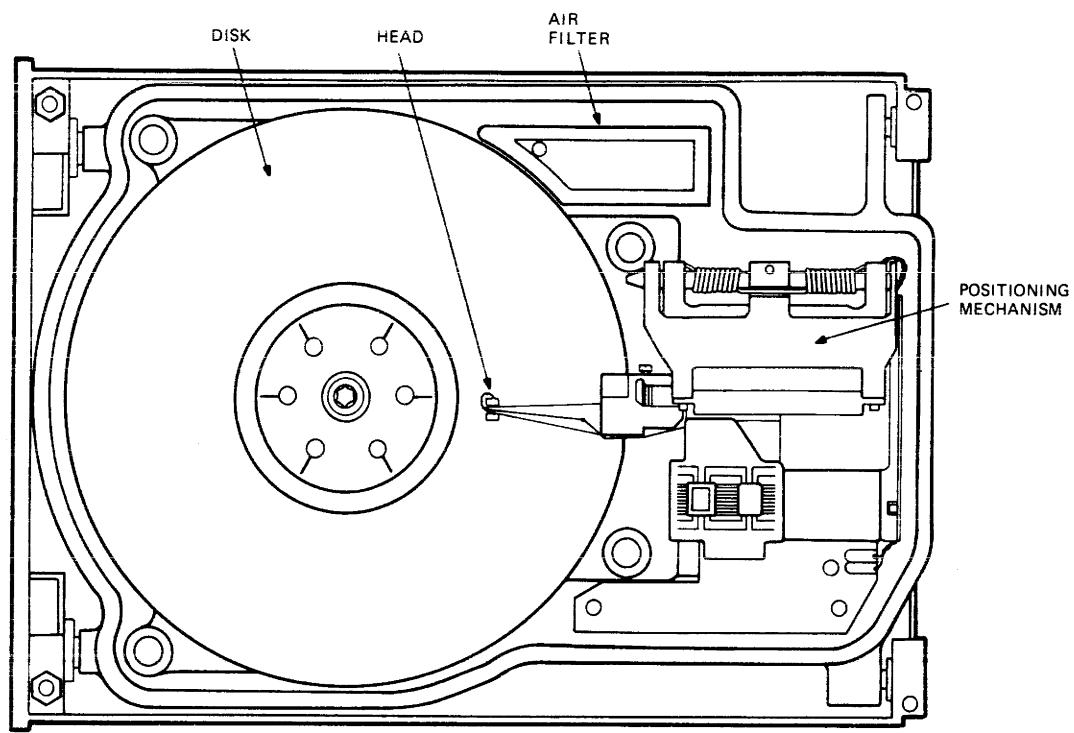

| 9.7.1   | RD52-A Drive Mechanism .....                  | 9-8  |

| 9.7.1.1 | Base Casting .....                            | 9-8  |

| 9.7.1.2 | DC Spindle Drive Motor .....                  | 9-8  |

| 9.7.1.3 | Disk Stack .....                              | 9-9  |

| 9.7.1.4 | Head Stack .....                              | 9-9  |

| 9.7.1.5 | Optical Encoder .....                         | 9-9  |

| 9.7.1.6 | Rotary Positioner .....                       | 9-9  |

| 9.7.1.7 | Automatic Actuator Lock .....                 | 9-9  |

| 9.7.2   | Electromagnetic Interference (EMI) Band ..... | 9-10 |

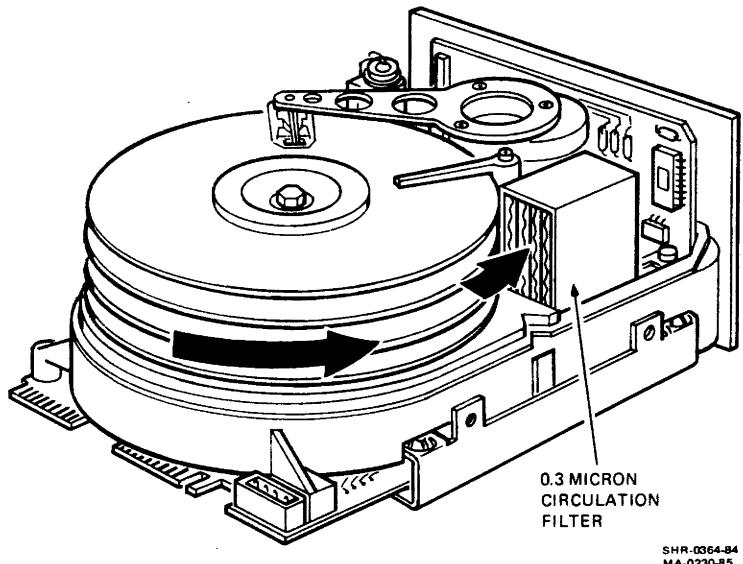

| 9.7.3   | Air Filtration .....                          | 9-10 |

|          |                                       |      |

|----------|---------------------------------------|------|

| 9.8      | Operation .....                       | 9-11 |

| 9.8.1    | Operator Functions .....              | 9-11 |

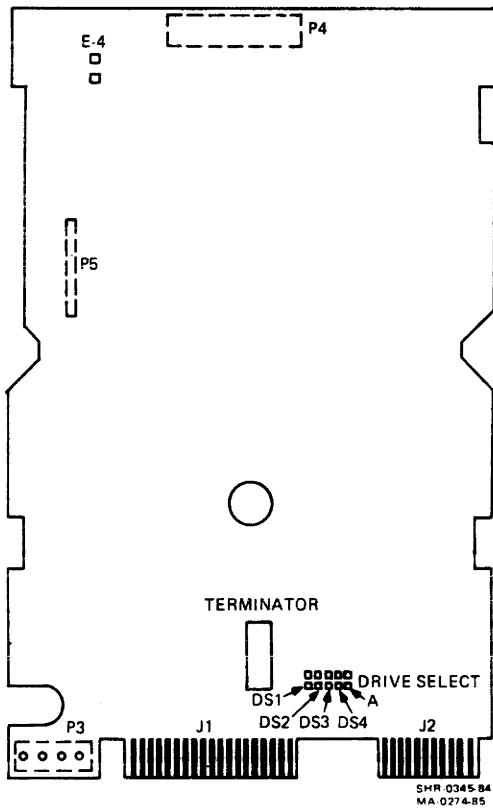

| 9.8.1.1  | Drive Select .....                    | 9-11 |

| 9.8.1.2  | Control Cable Termination .....       | 9-11 |

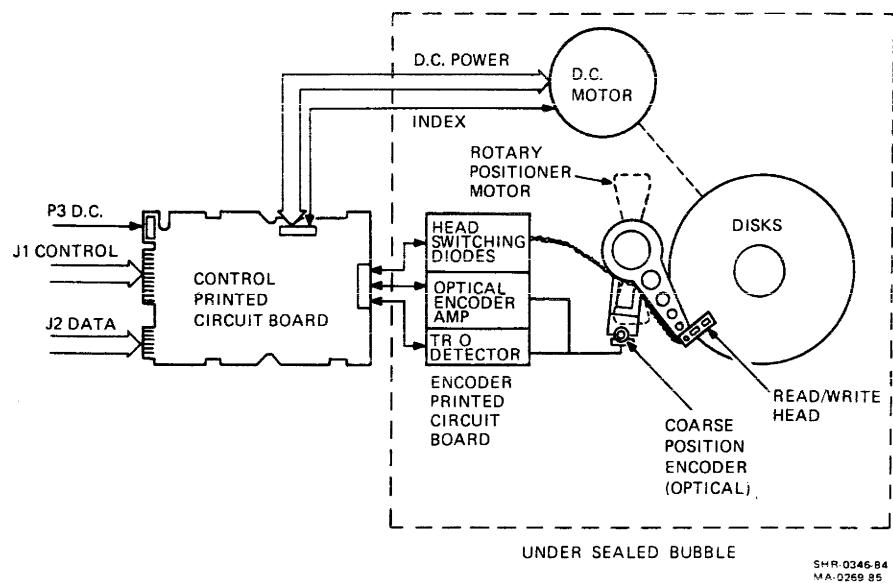

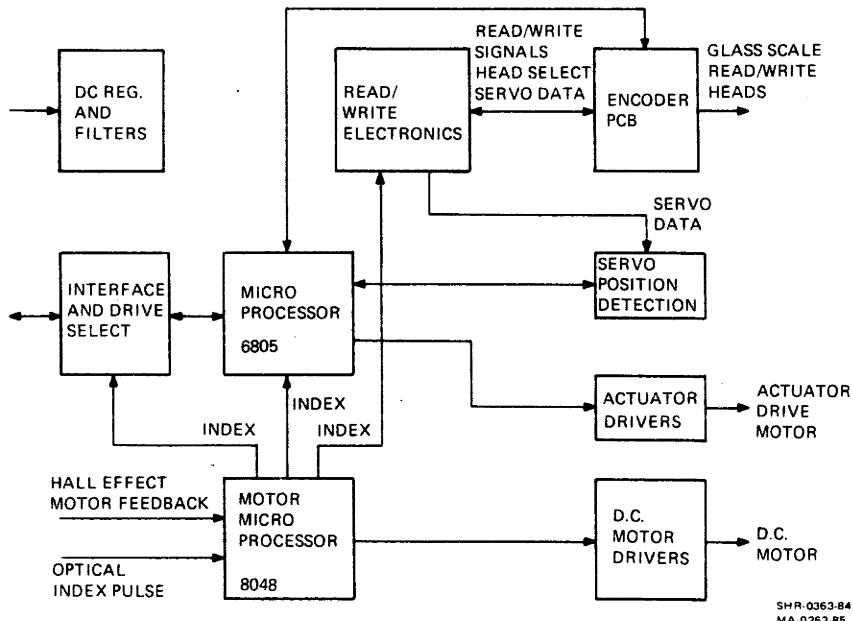

| 9.8.2    | Functional Description .....          | 9-12 |

| 9.8.3    | Drive Electronics .....               | 9-12 |

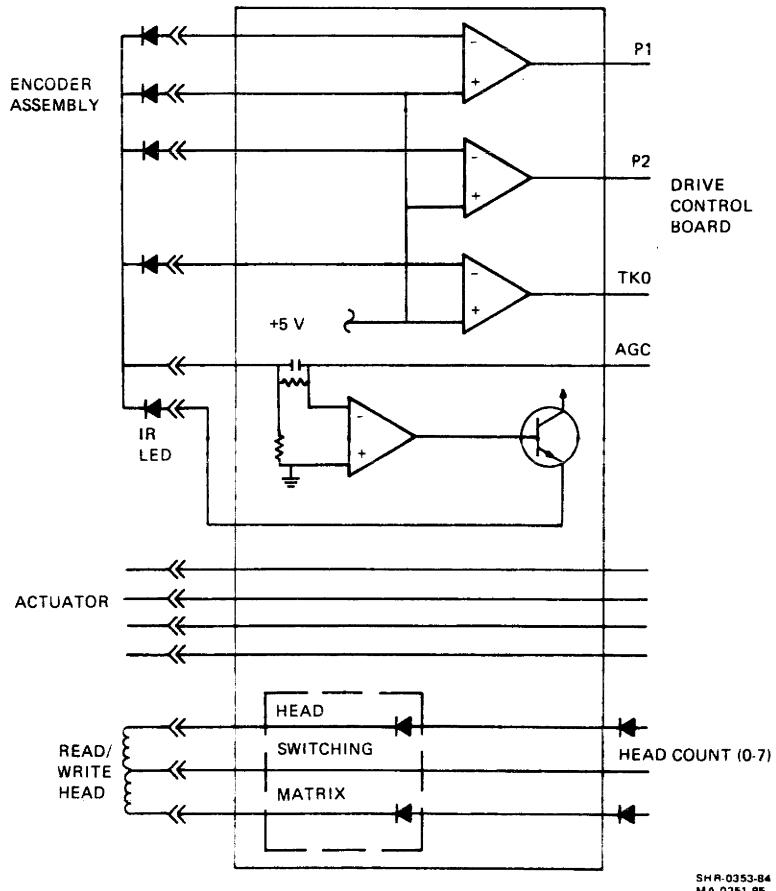

| 9.8.4    | Encoder PCB .....                     | 9-14 |

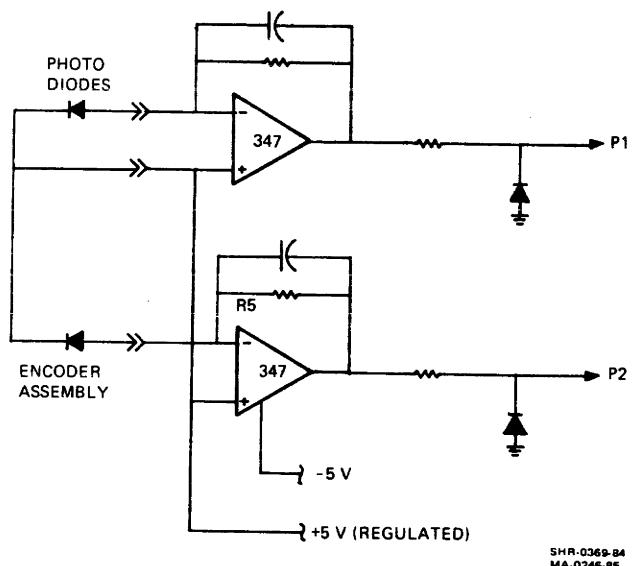

| 9.8.4.1  | AGC Circuit .....                     | 9-14 |

| 9.8.4.2  | P1 and P2 Signal Generation .....     | 9-14 |

| 9.8.4.3  | Track 0 .....                         | 9-16 |

| 9.8.5    | Drive Control PCB .....               | 9-16 |

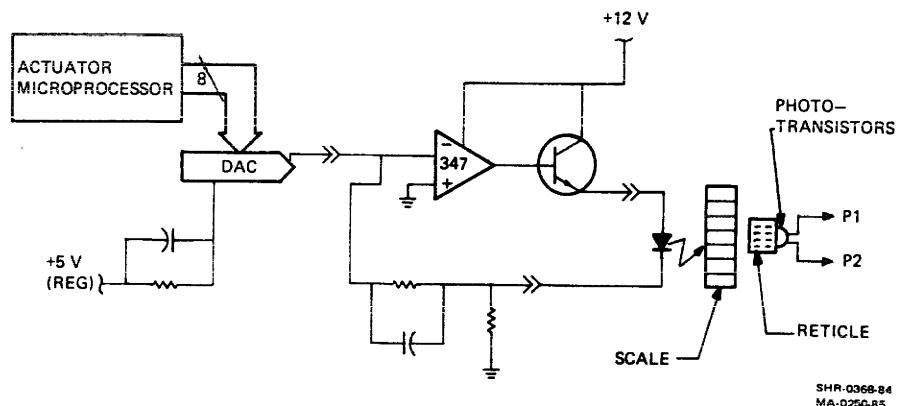

| 9.8.6    | Actuator Positioning Circuits .....   | 9-18 |

| 9.8.6.1  | Actuator Microprocessor .....         | 9-18 |

| 9.8.6.2  | Recalibration .....                   | 9-18 |

| 9.8.6.3  | AGC Function .....                    | 9-18 |

| 9.8.6.4  | On Track Servoing (Coarse) .....      | 9-18 |

| 9.8.6.5  | Fine Servoing .....                   | 9-18 |

| 9.8.6.6  | Ramped Mode Seeking .....             | 9-18 |

| 9.8.6.7  | Slew Mode Seeking .....               | 9-18 |

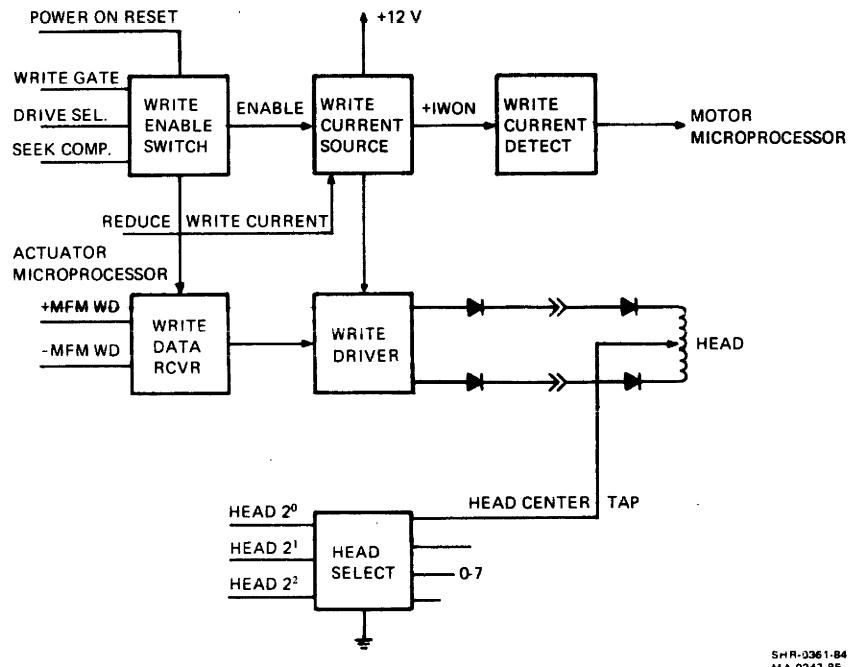

| 9.8.7    | Write Data Circuits .....             | 9-19 |

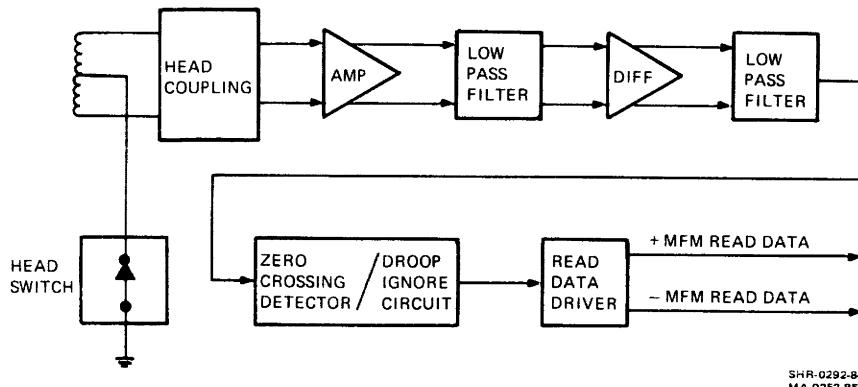

| 9.8.8    | Read Data Circuits .....              | 9-20 |

| 9.8.8.1  | Low Pass Filter/Differentiator .....  | 9-20 |

| 9.8.8.2  | Zero Crossing Detector .....          | 9-20 |

| 9.8.8.3  | Droop Ignore Circuit .....            | 9-20 |

| 9.8.9    | Motor Microprocessor .....            | 9-21 |

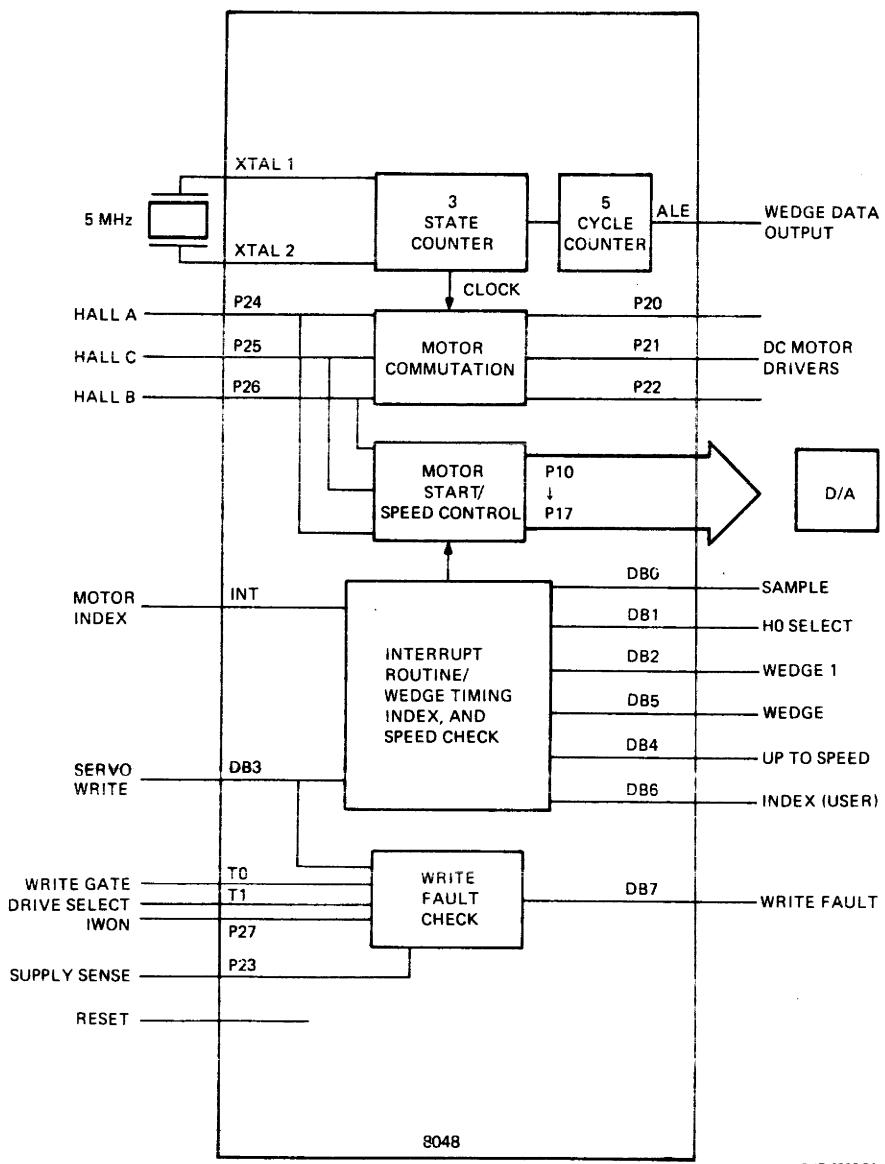

| 9.8.9.1  | Description .....                     | 9-21 |

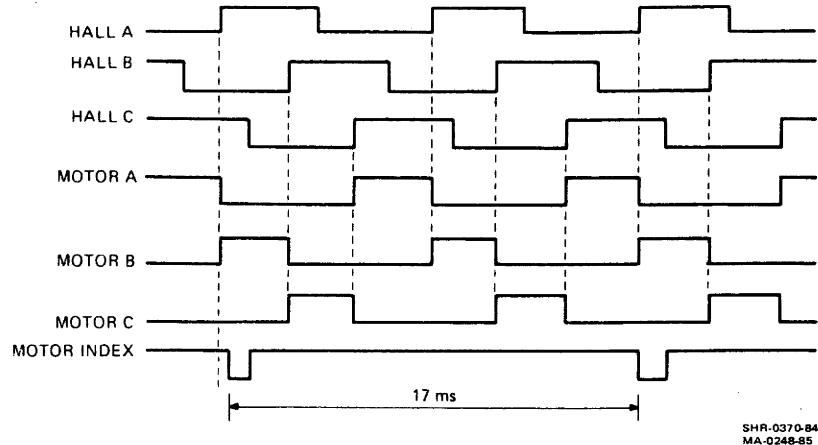

| 9.8.9.2  | DC Motor Control .....                | 9-22 |

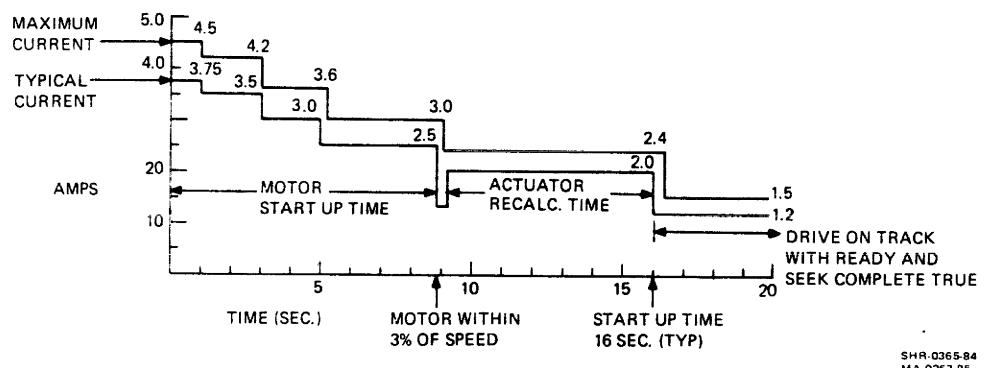

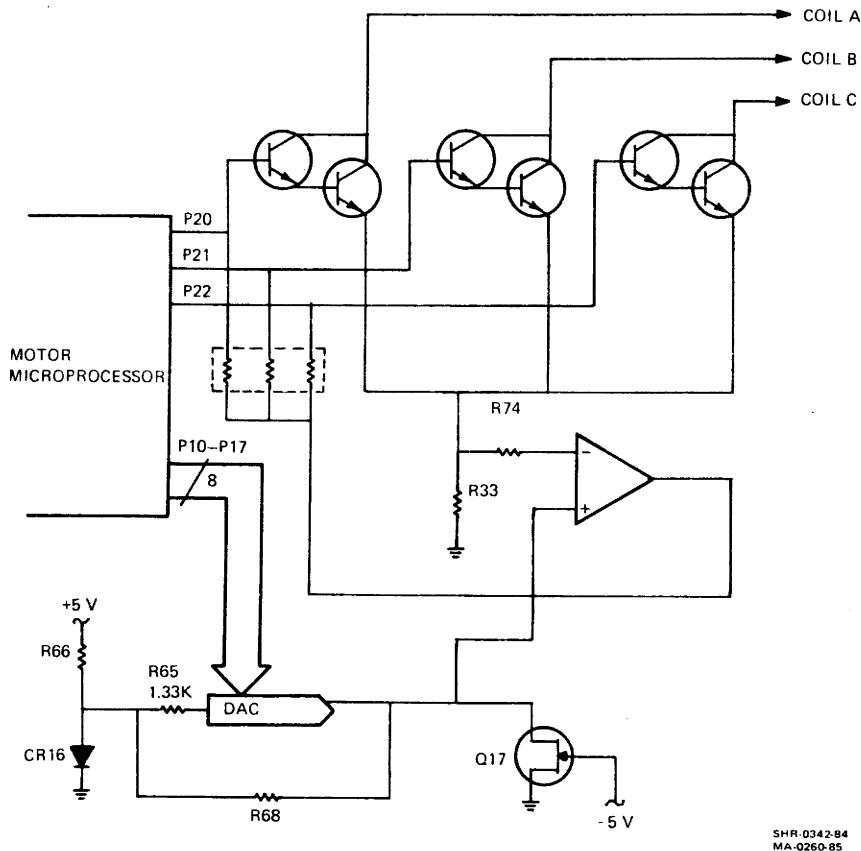

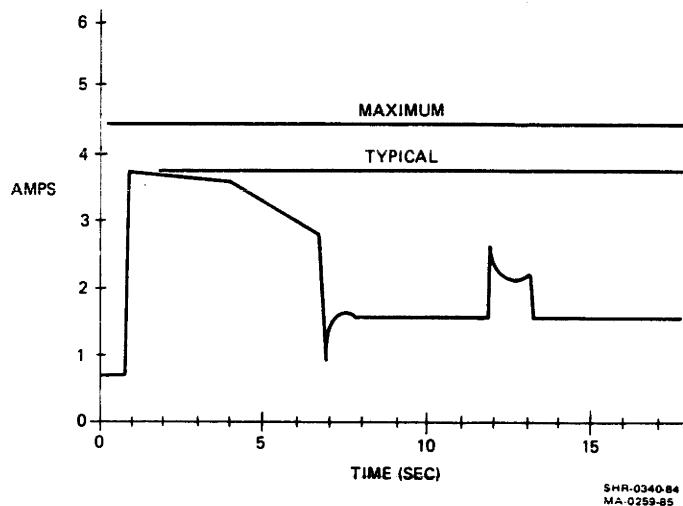

| 9.8.9.3  | Motor Current .....                   | 9-22 |

| 9.8.9.4  | DC Motor Drive Circuit .....          | 9-24 |

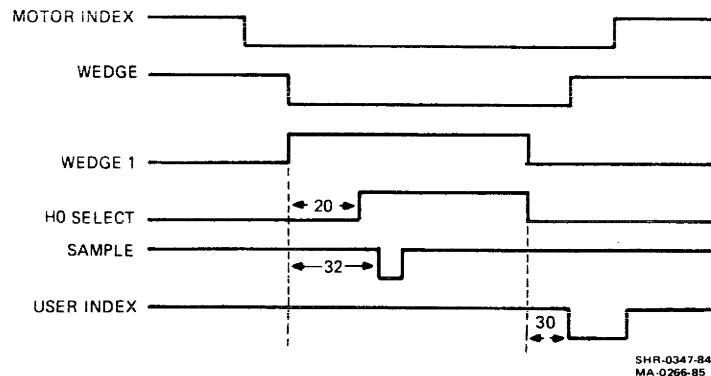

| 9.8.9.5  | WEDGE and INDEX Signals .....         | 9-25 |

| 9.8.9.6  | WRITE FAULT .....                     | 9-25 |

| 9.8.9.7  | Power Faults .....                    | 9-25 |

| 9.9      | Interface .....                       | 9-26 |

| 9.9.1    | Control Signal Interface .....        | 9-26 |

| 9.9.1.1  | General Description .....             | 9-26 |

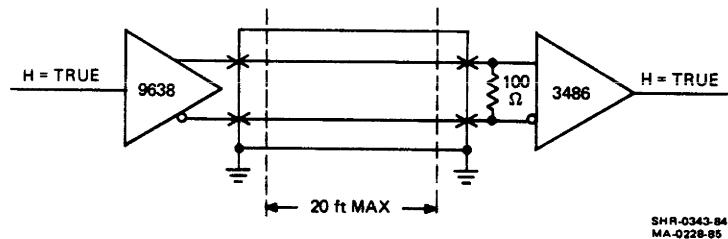

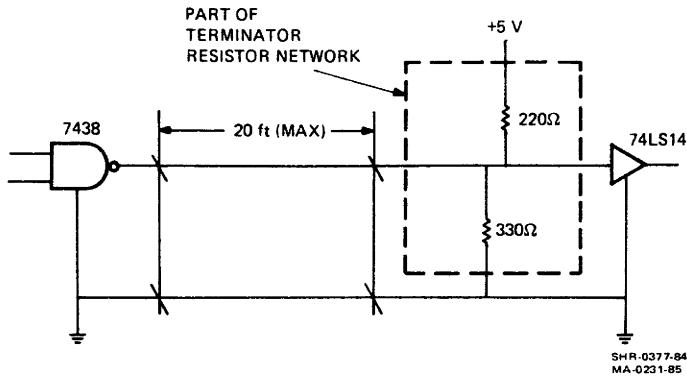

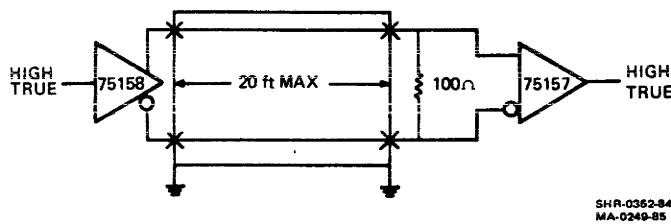

| 9.9.1.2  | Driver/Receiver .....                 | 9-28 |

| 9.9.1.3  | Control Signal Descriptions .....     | 9-28 |

| 9.9.2    | Data Signal Interface .....           | 9-30 |

| 9.9.2.1  | General Description .....             | 9-30 |

| 9.9.2.2  | Driver/Receiver .....                 | 9-30 |

| 9.9.2.3  | Data Signal Descriptions .....        | 9-32 |

| 9.10     | RD52-A (30-23227-02) Disk Drive ..... | 9-32 |

| 9.10.1   | General .....                         | 9-32 |

| 9.10.2   | Specifications .....                  | 9-32 |

| 9.10.2.1 | Physical Specifications .....         | 9-32 |

| 9.10.2.2 | Performance Specifications .....      | 9-34 |

| 9.10.2.3 | Functional Specifications .....       | 9-34 |

| 9.10.3   | Power Requirements .....              | 9-35 |

| 9.10.3.1 | DC Power .....                        | 9-35 |

| 9.10.3.2 | DC Power Connector .....              | 9-35 |

|          |                                           |      |

|----------|-------------------------------------------|------|

| 9.11     | Physical Description .....                | 9-36 |

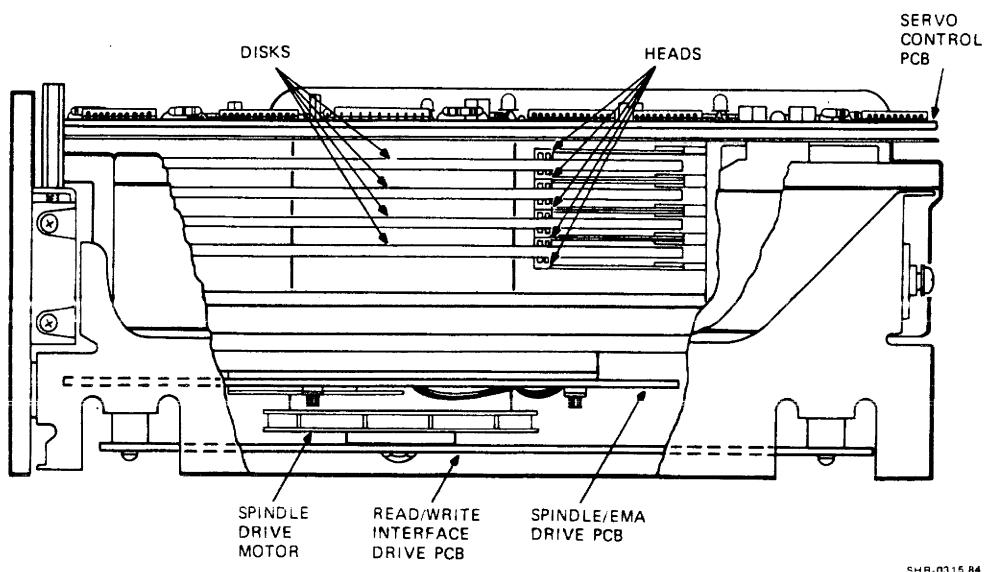

| 9.11.1   | Assemblies .....                          | 9-36 |

| 9.11.1.1 | Read/Write Interface PCB .....            | 9-36 |

| 9.11.1.2 | Spindle/EMA Drive PCB .....               | 9-36 |

| 9.11.1.3 | Servo Control PCB .....                   | 9-36 |

| 9.11.1.4 | Spindle Drive Mechanism .....             | 9-36 |

| 9.11.1.5 | Positioning Mechanism .....               | 9-36 |

| 9.11.1.6 | Read/Write Heads and Media .....          | 9-38 |

| 9.11.2   | Air Filtration System .....               | 9-38 |

| 9.12     | Operation .....                           | 9-38 |

| 9.12.1   | Operator Functions .....                  | 9-38 |

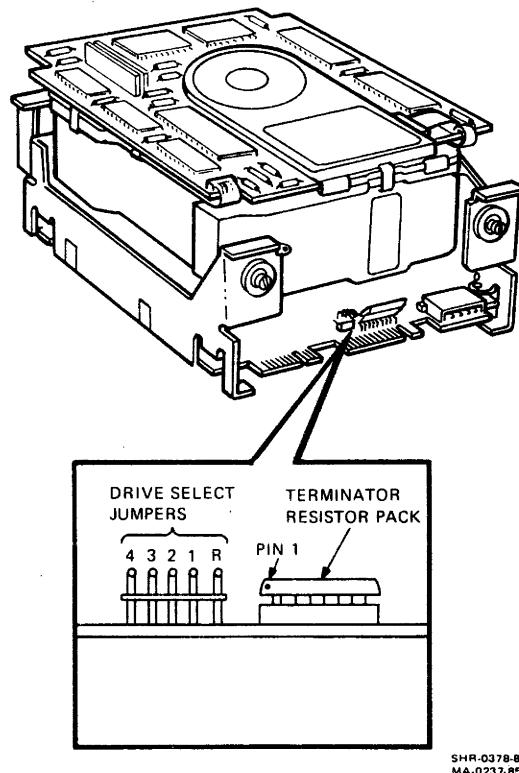

| 9.12.1.1 | Drive Select .....                        | 9-38 |

| 9.12.1.2 | Control Cable Termination .....           | 9-38 |

| 9.12.2   | Drive Organization .....                  | 9-39 |

| 9.12.3   | Power Sequencing .....                    | 9-39 |

| 9.12.4   | Microprocessor Wake-Up Timing .....       | 9-39 |

| 9.12.4.1 | Spindle Open Loop Acceleration Ramp ..... | 9-39 |

| 9.12.4.2 | Spindle Driver .....                      | 9-40 |

| 9.12.4.3 | Servo Control of the Spindle .....        | 9-40 |

| 9.12.4.4 | Watch-Dog Inhibitor .....                 | 9-40 |

| 9.12.4.5 | Actuator Disabling .....                  | 9-41 |

| 9.12.4.6 | Carriage Latch Release .....              | 9-41 |

| 9.12.4.7 | Automatic Rezero Routine .....            | 9-41 |

| 9.12.5   | Fault Finding .....                       | 9-41 |

| 9.12.5.1 | Error Detection .....                     | 9-41 |

| 9.12.5.2 | Power Fault Status Inhibitor .....        | 9-41 |

| 9.12.5.3 | Power Faults .....                        | 9-42 |

| 9.12.6   | Interface Operations .....                | 9-43 |

| 9.12.7   | Interface Logic .....                     | 9-45 |

| 9.12.8   | Servo Operations .....                    | 9-46 |

| 9.12.8.1 | Velocity Loop .....                       | 9-46 |

| 9.12.8.2 | Servo Status Reporting .....              | 9-46 |

| 9.12.8.3 | Window Generator .....                    | 9-47 |

| 9.12.8.4 | Index Reporting .....                     | 9-47 |

| 9.12.8.5 | Servo AGC Circuit .....                   | 9-47 |

| 9.12.8.6 | EMA Driver Circuit .....                  | 9-47 |

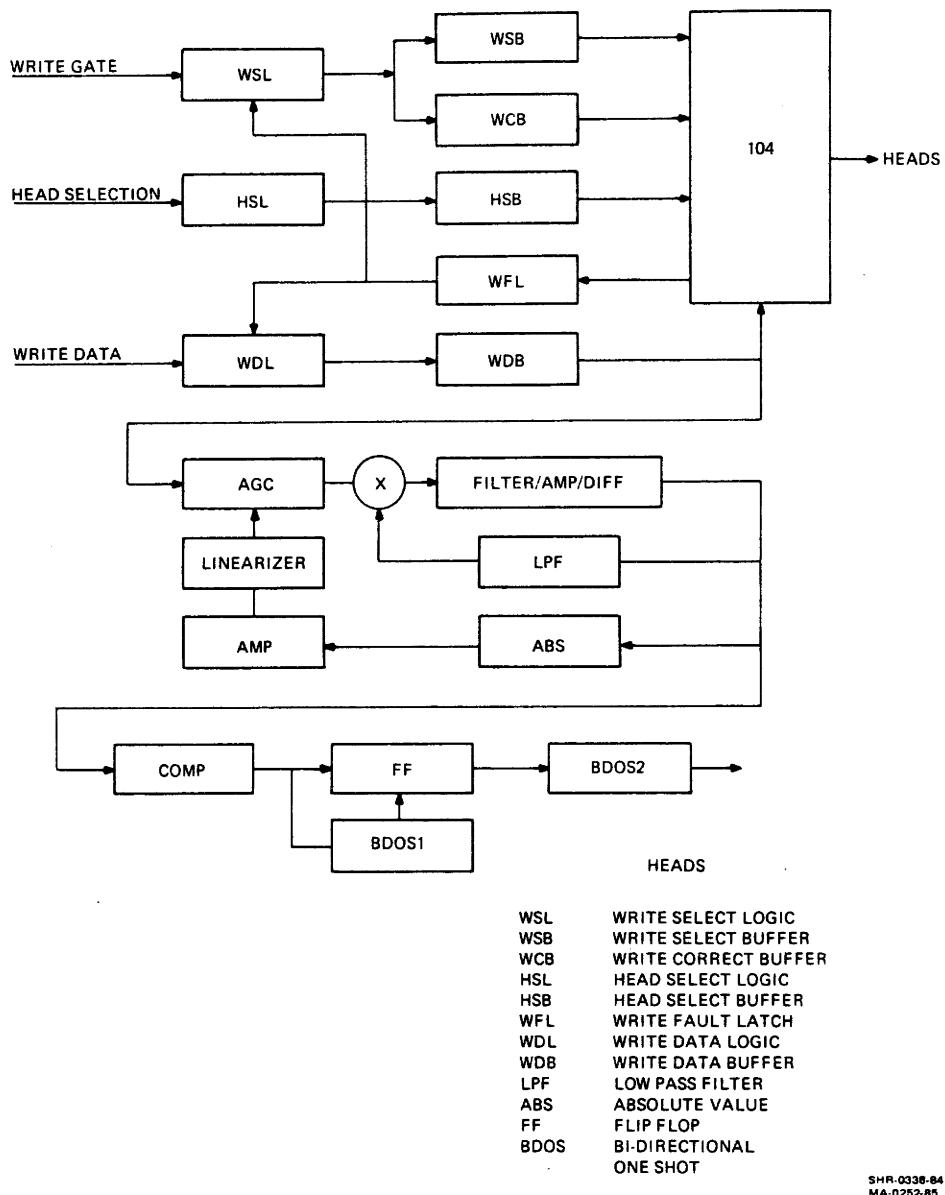

| 9.12.9   | Read/Write Operations .....               | 9-47 |

| 9.12.9.1 | Write Operations .....                    | 9-49 |

| 9.12.9.2 | Read Operations .....                     | 9-49 |

| 9.12.9.3 | Read Channel/Analog .....                 | 9-49 |

| 9.12.9.4 | Read Channel Digital .....                | 9-49 |

| 9.13     | Interface .....                           | 9-50 |

| 9.13.1   | Interface Connectors .....                | 9-50 |

| 9.13.2   | Control Signal Interface .....            | 9-50 |

| 9.13.2.1 | General .....                             | 9-50 |

| 9.13.2.2 | Driver/Receiver .....                     | 9-52 |

| 9.13.2.3 | Control Signal Descriptions .....         | 9-52 |

| 9.13.3   | Data Interface Signals .....              | 9-54 |

| 9.13.3.1 | General .....                             | 9-54 |

| 9.13.3.2 | Driver/Receiver .....                     | 9-54 |

| 9.13.3.3 | Data Signal Descriptions .....            | 9-55 |

## APPENDIX A    DIAGNOSTIC, ERROR, AND DEVICE CODES

### FIGURES

|      |                                                                                              |      |

|------|----------------------------------------------------------------------------------------------|------|

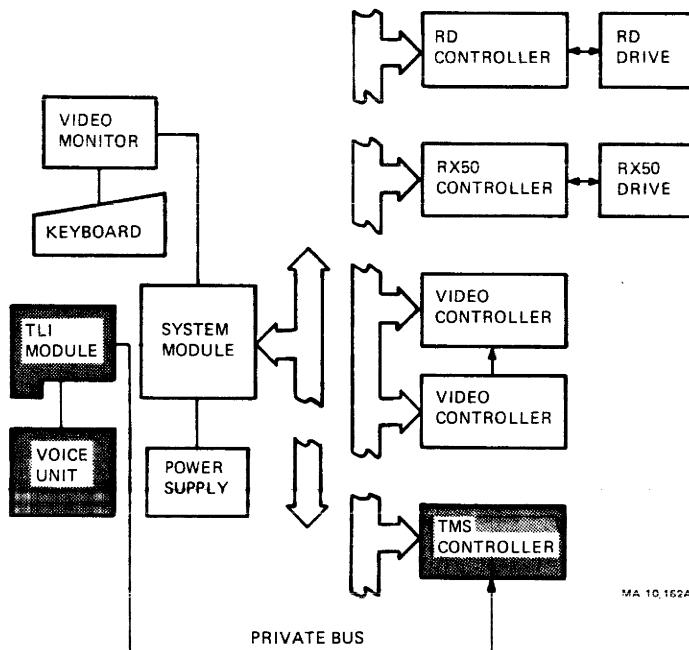

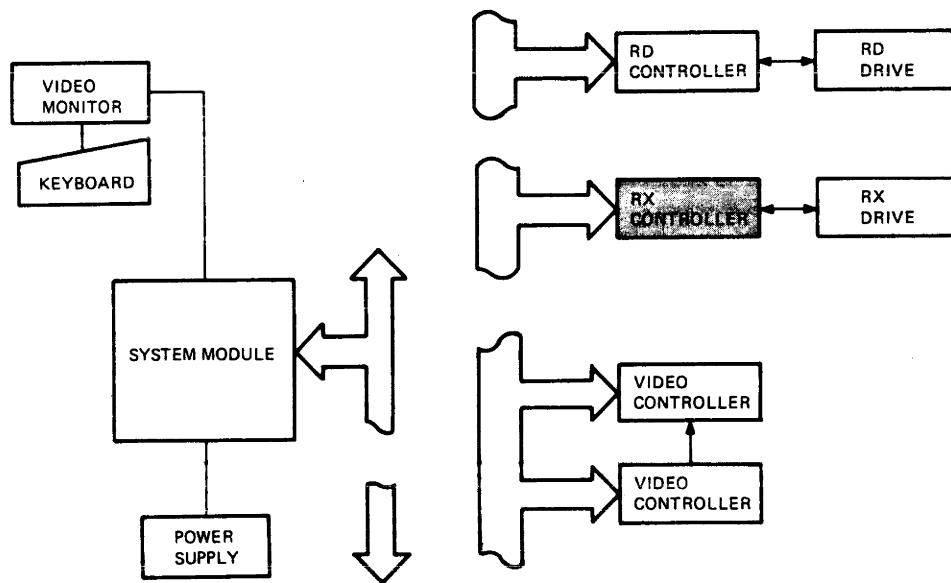

| 1-1  | The Professional 300 Series Block Diagram .....                                              | 1-1  |

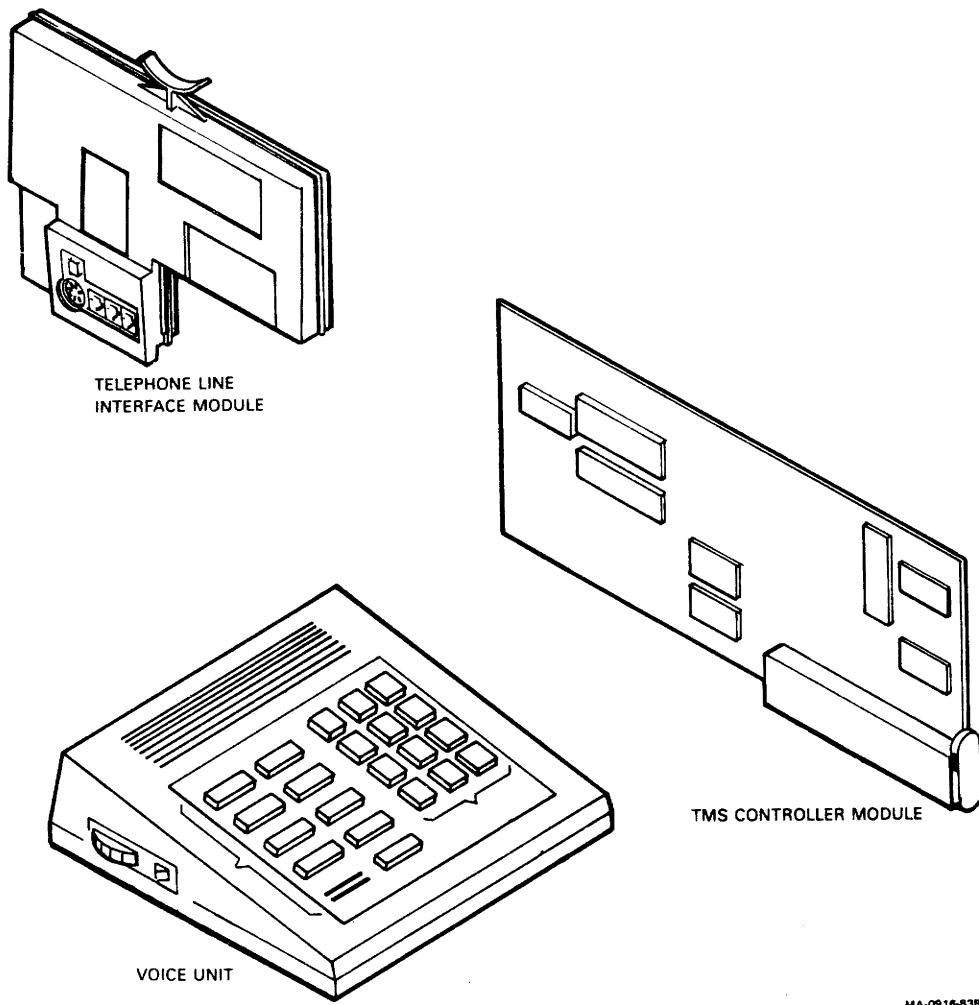

| 1-2  | TMS Hardware Components .....                                                                | 1-2  |

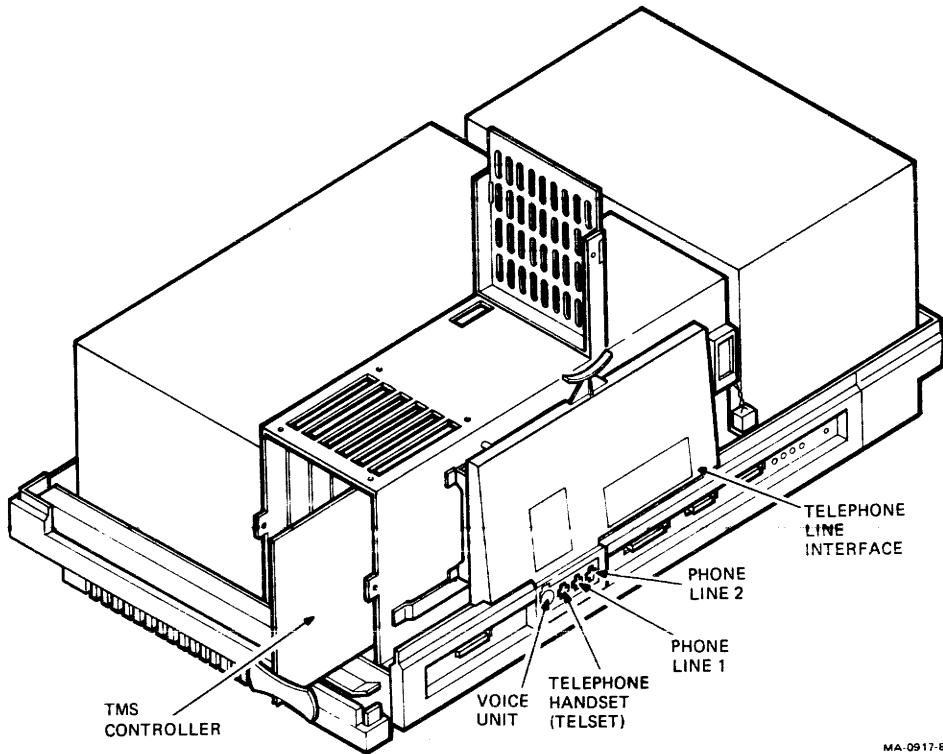

| 1-3  | TMS Module Installation .....                                                                | 1-3  |

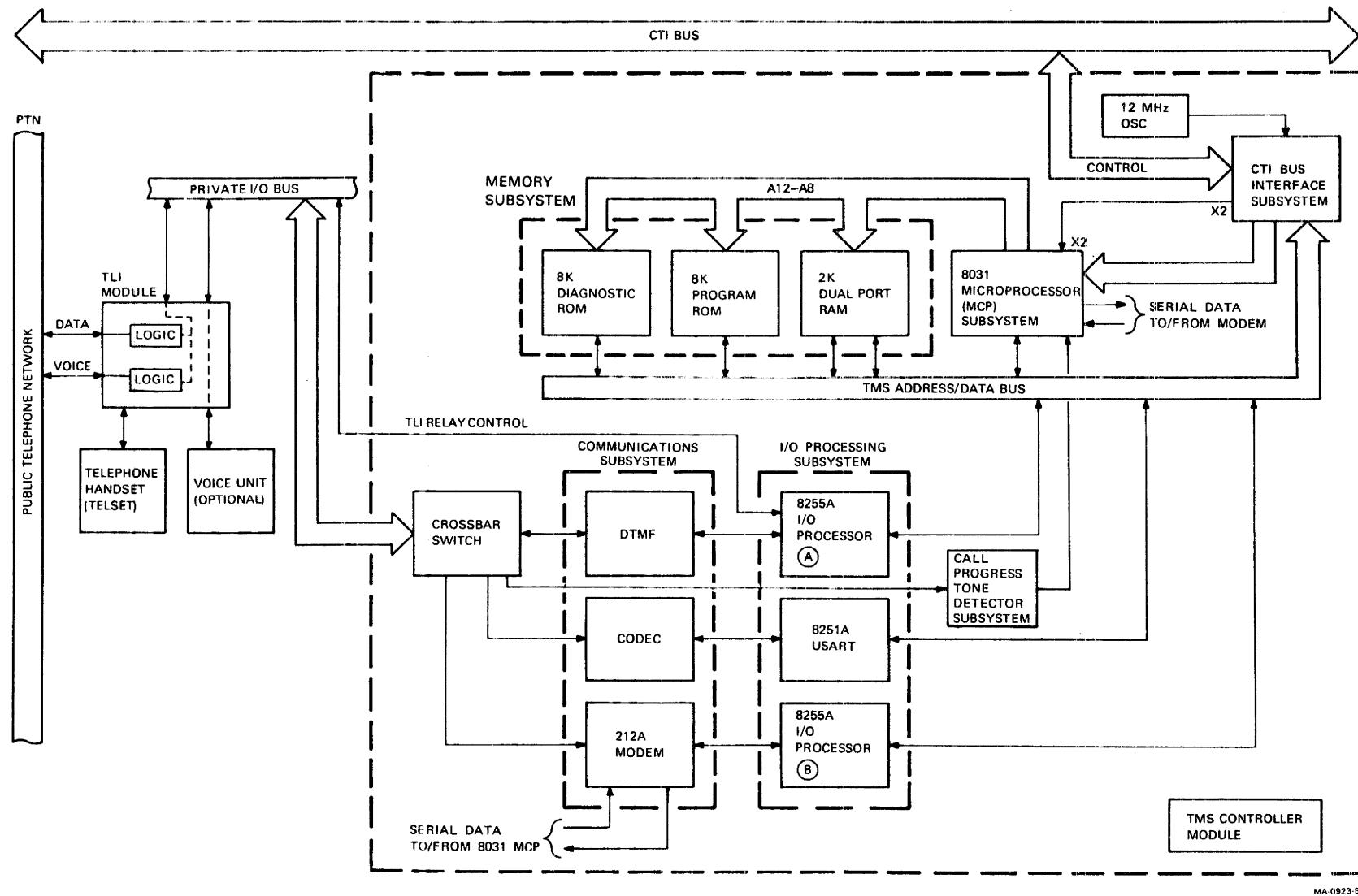

| 1-4  | Telephone Management System (TMS) Block Diagram .....                                        | 1-5  |

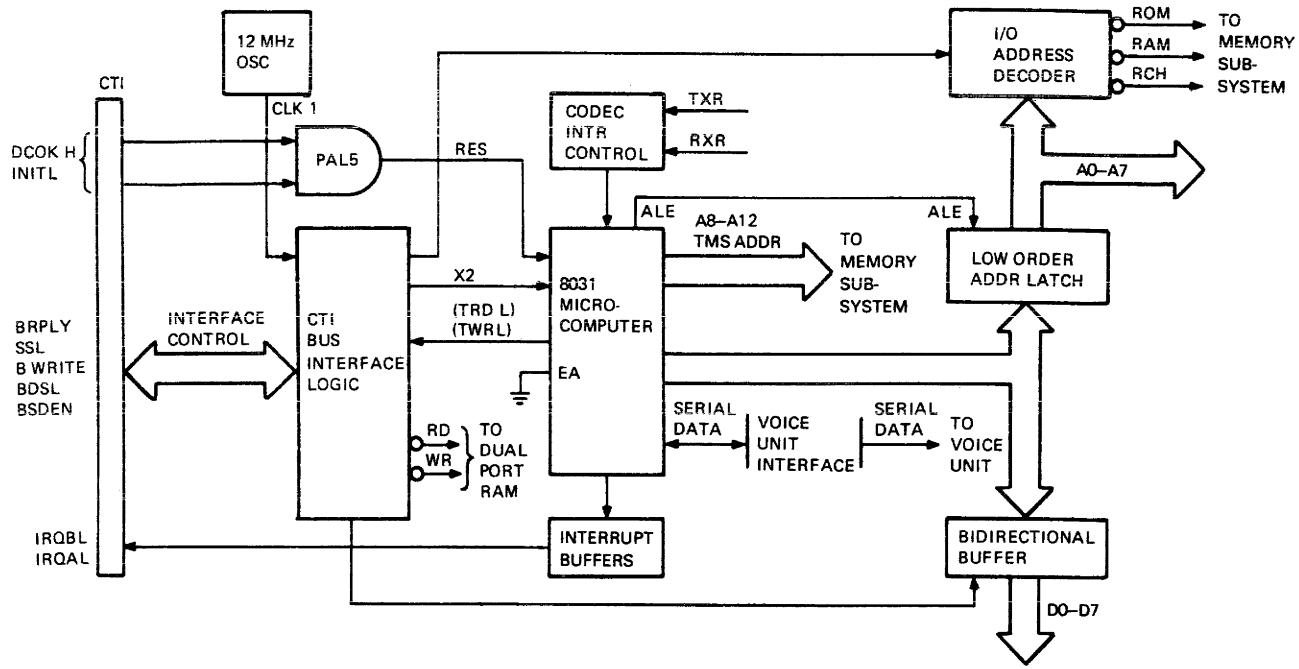

| 1-5  | 8031 Microprocessor Subsystem .....                                                          | 1-11 |

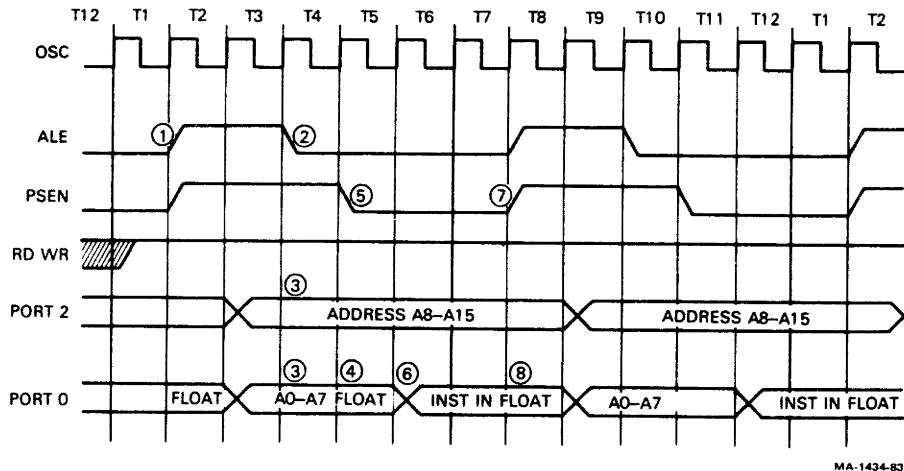

| 1-6  | Program Memory Read Cycle Timing .....                                                       | 1-12 |

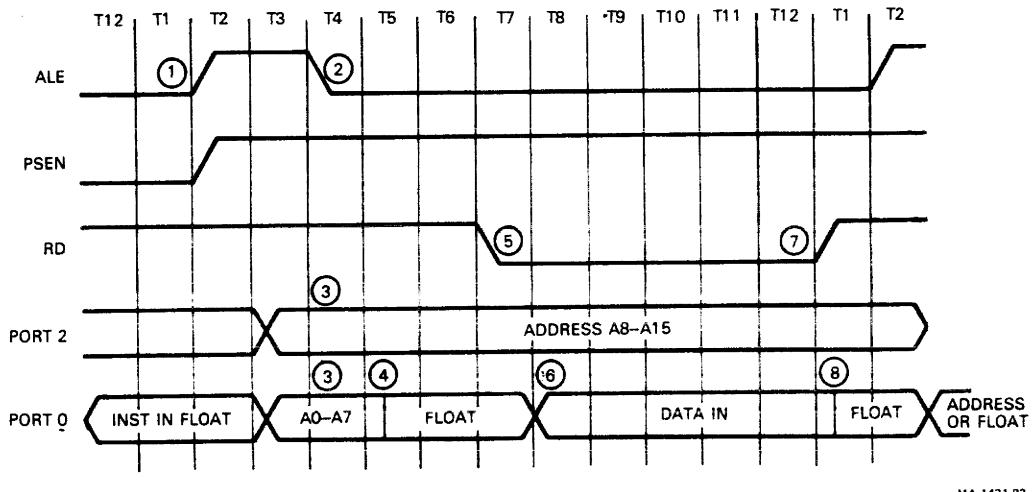

| 1-7  | Data Memory Read Cycle Timing .....                                                          | 1-13 |

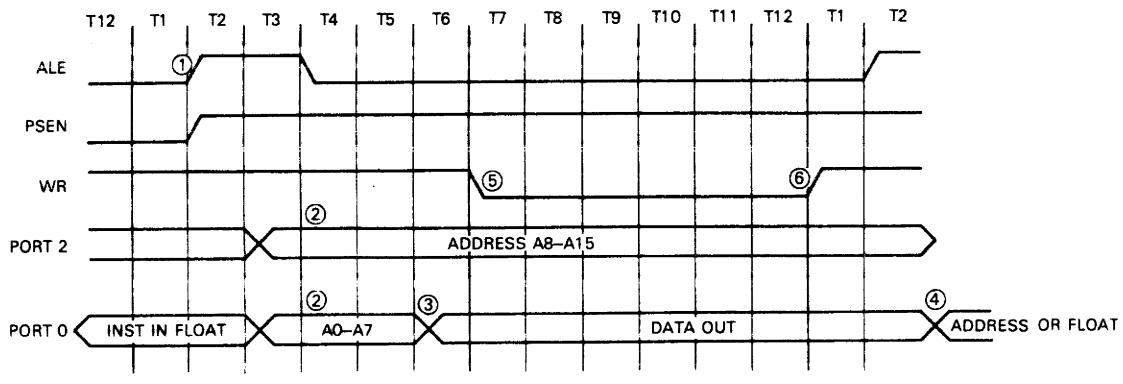

| 1-8  | Data Memory Write Cycle Timing .....                                                         | 1-13 |

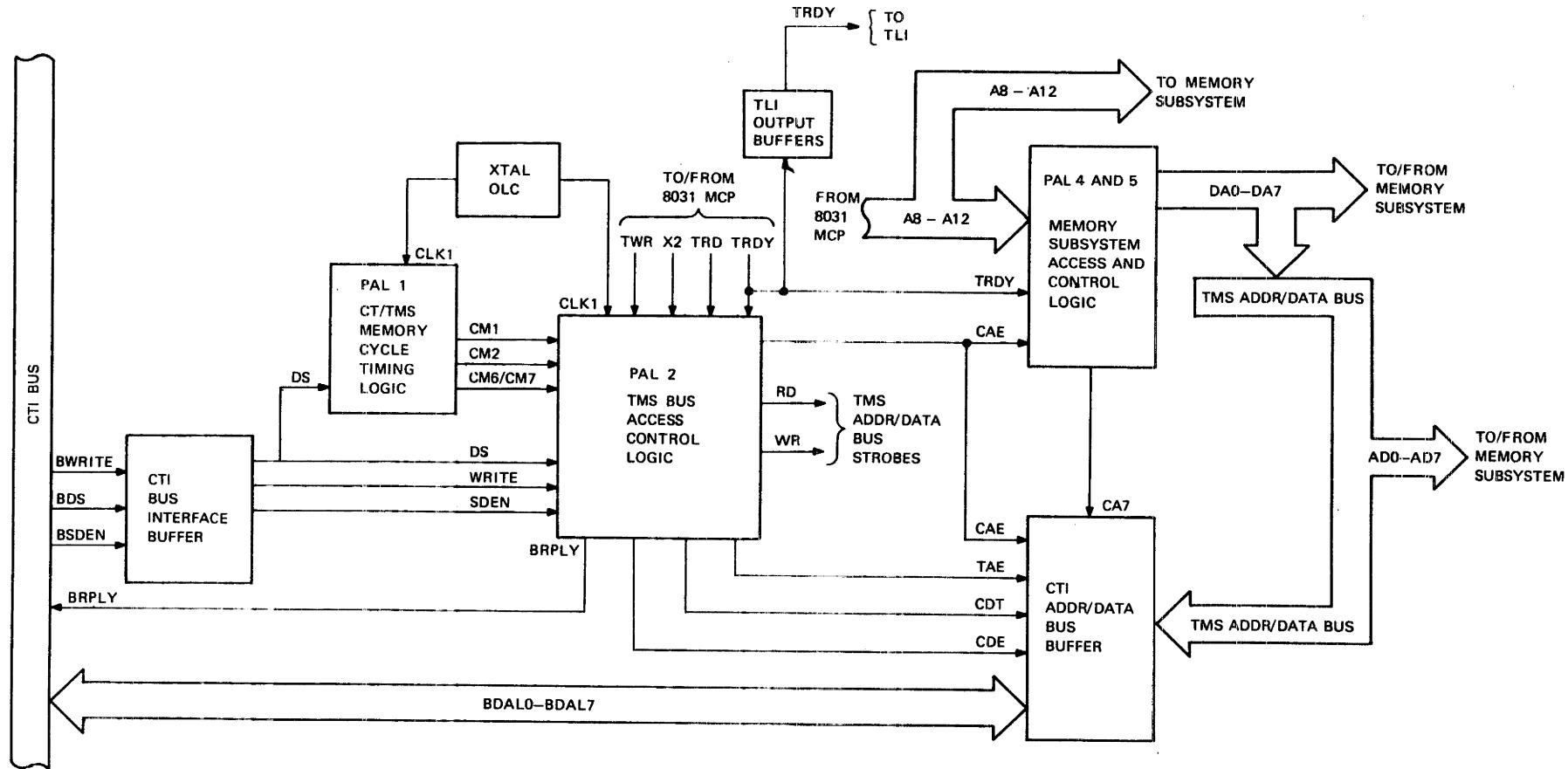

| 1-9  | CTI Bus Interface Circuit Subsystem .....                                                    | 1-15 |

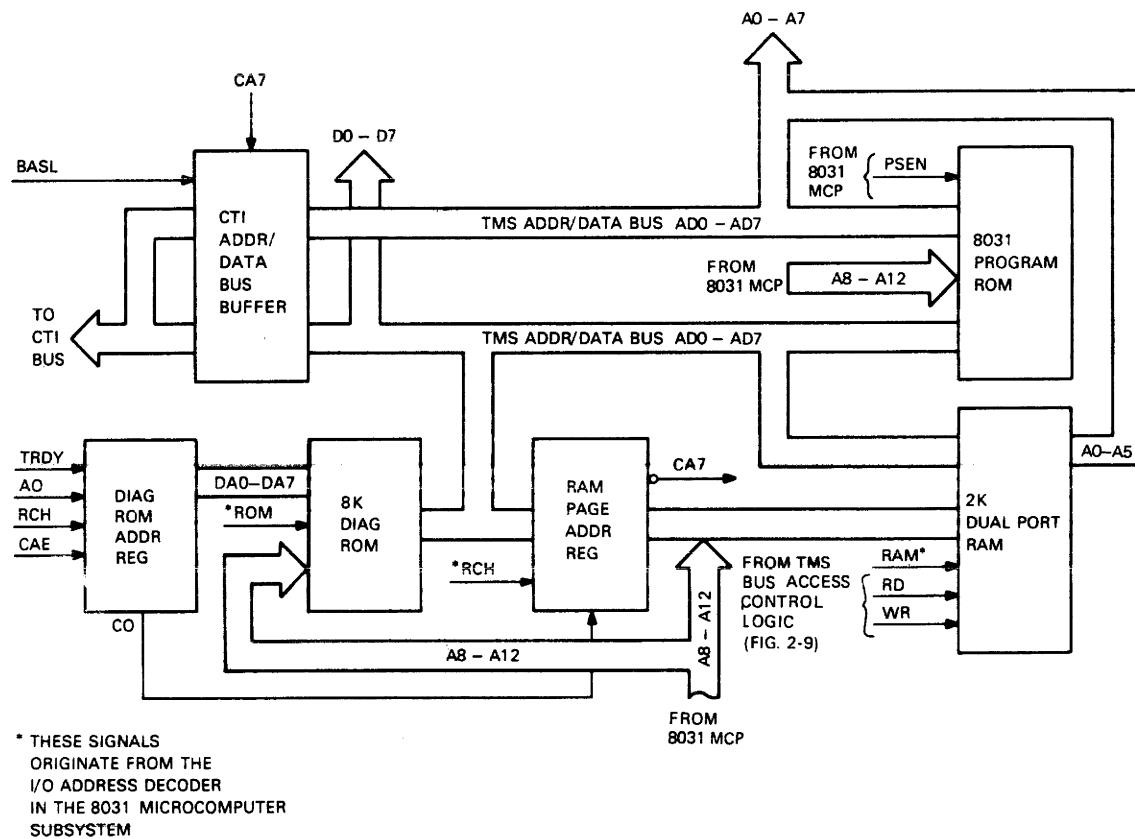

| 1-10 | Memory Subsystem .....                                                                       | 1-17 |

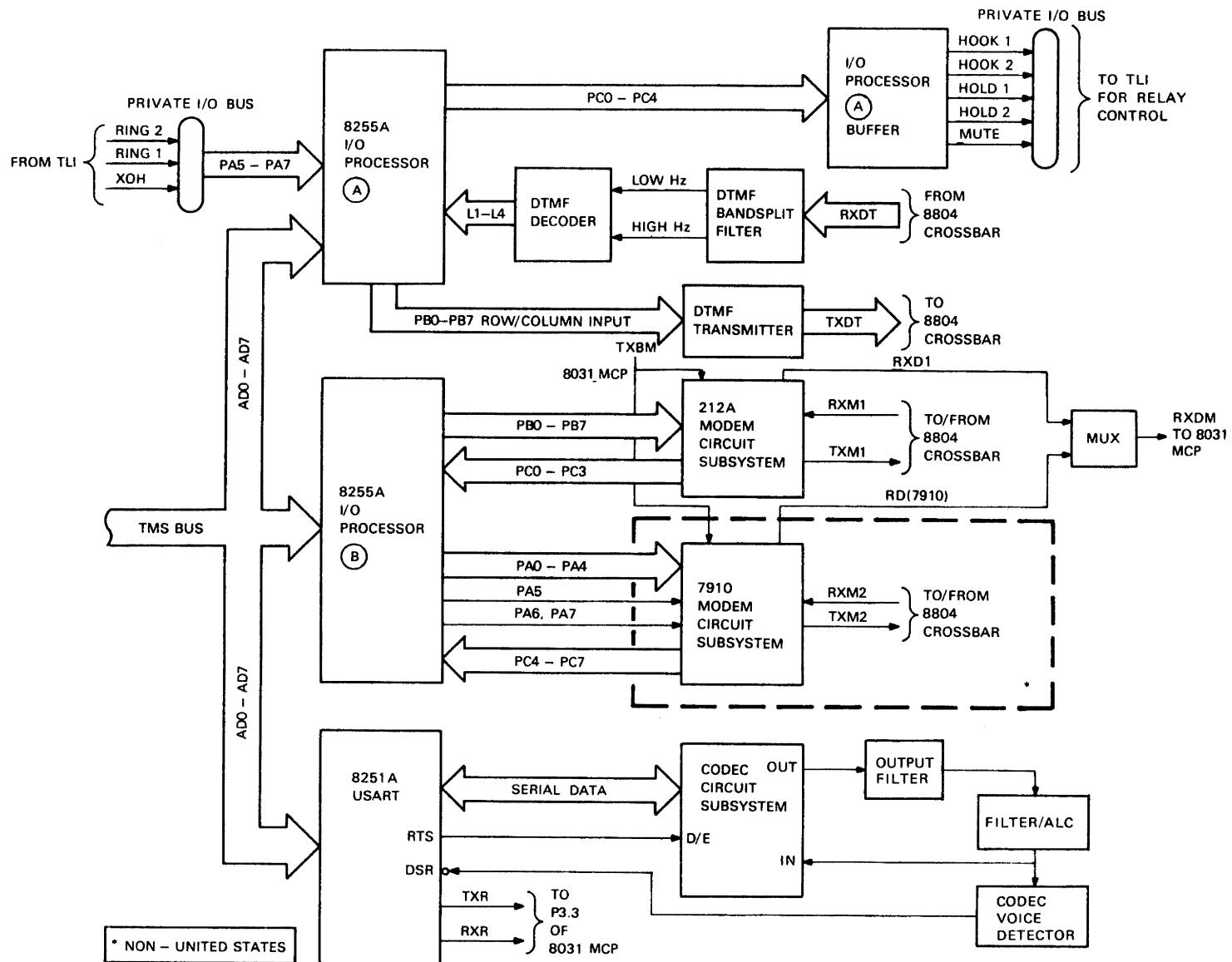

| 1-11 | I/O Processing Subsystem .....                                                               | 1-20 |

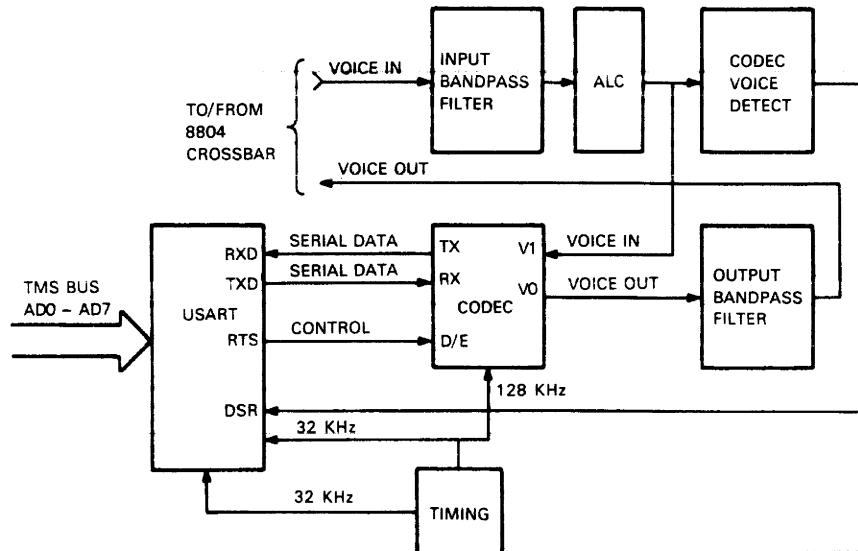

| 1-12 | CODEC Circuit Subsystem .....                                                                | 1-21 |

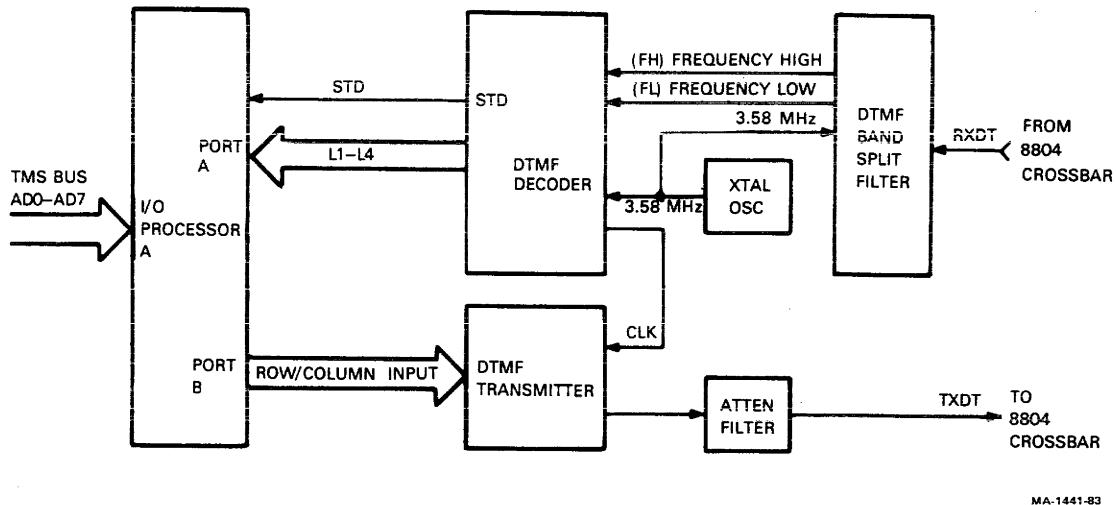

| 1-13 | DTMF Circuit Subsystem .....                                                                 | 1-23 |

| 1-14 | 212A Modem Circuit Subsystem .....                                                           | 1-26 |

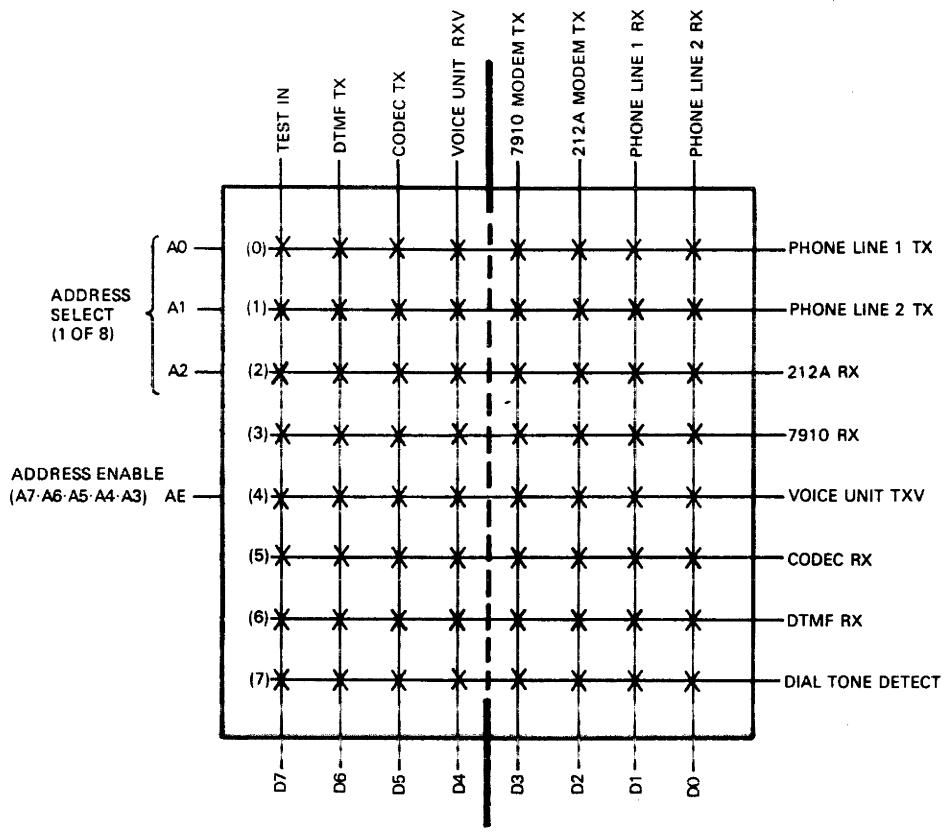

| 1-15 | Crossbar Signal Switch Functional Diagram .....                                              | 1-31 |

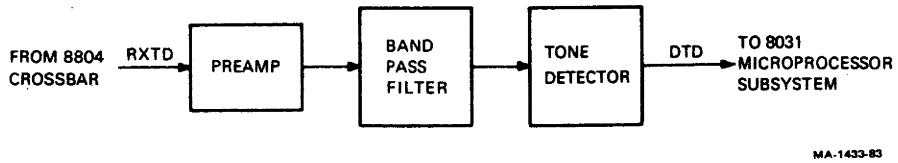

| 1-16 | Call Progress Tone Detector Functional Diagram .....                                         | 1-32 |

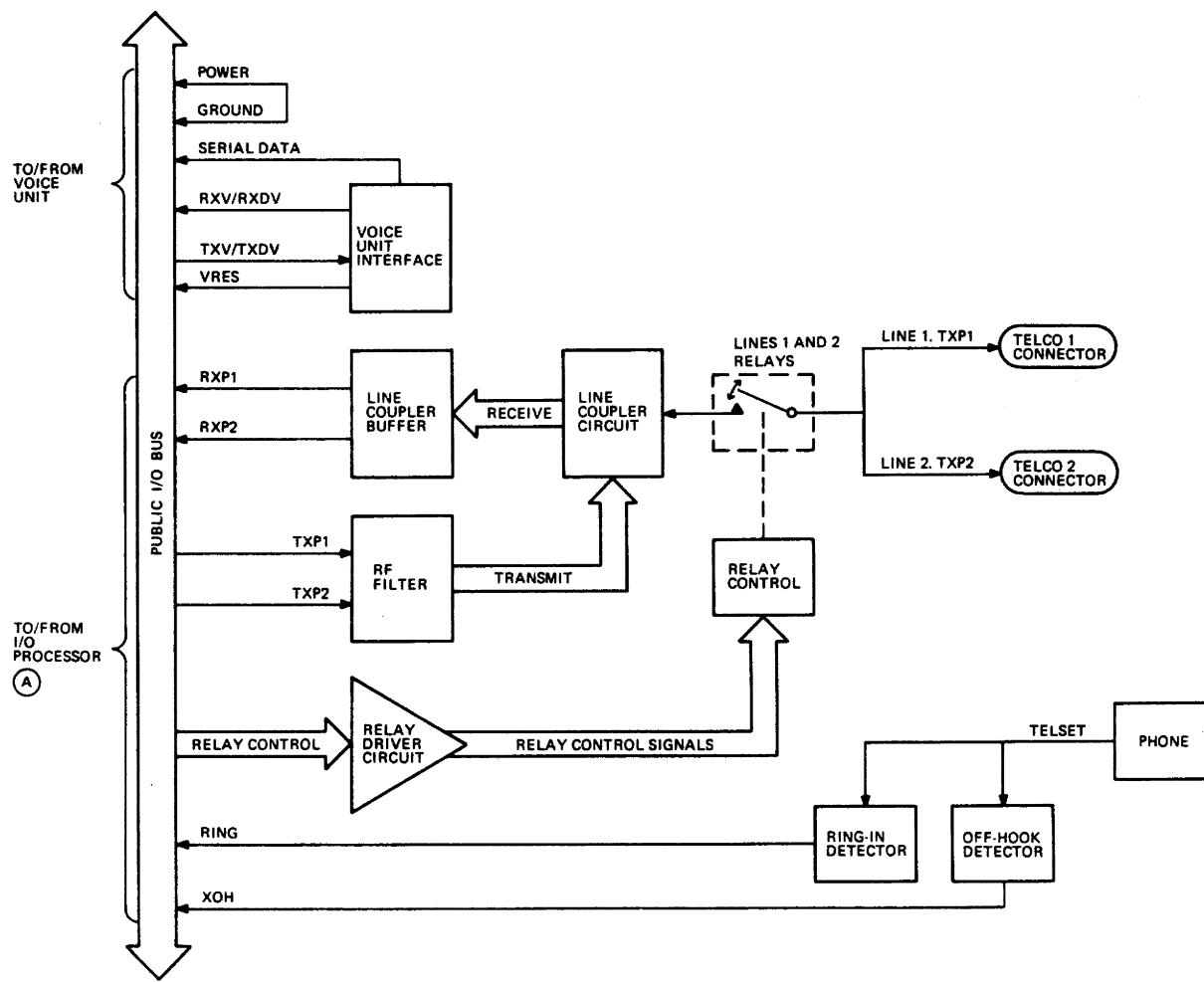

| 1-17 | TLI Module Functional Diagram .....                                                          | 1-34 |

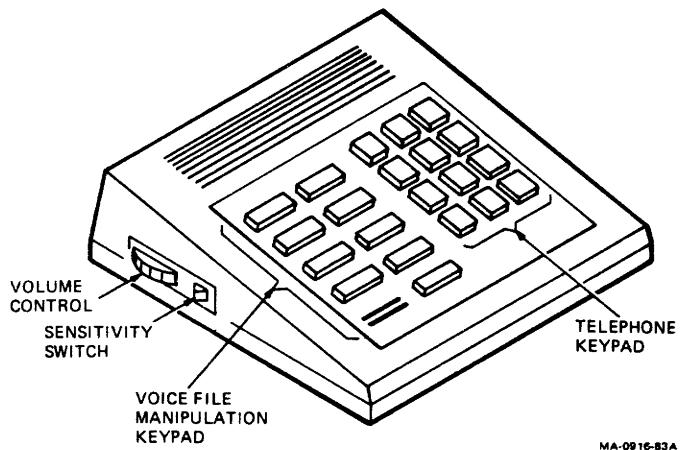

| 1-18 | DTC11-B Voice Unit .....                                                                     | 1-36 |

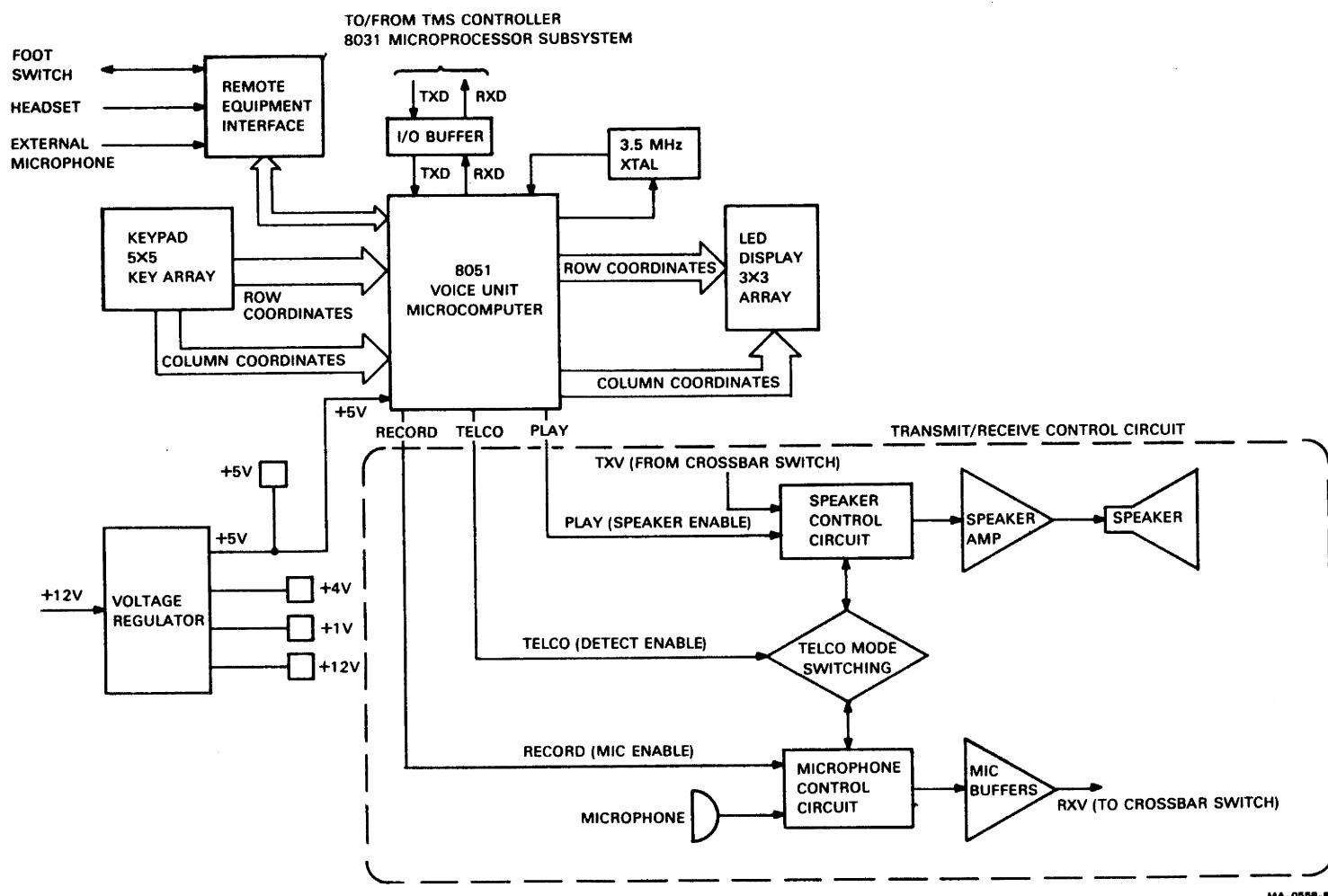

| 1-19 | Voice Unit Functional Block Diagram .....                                                    | 1-38 |

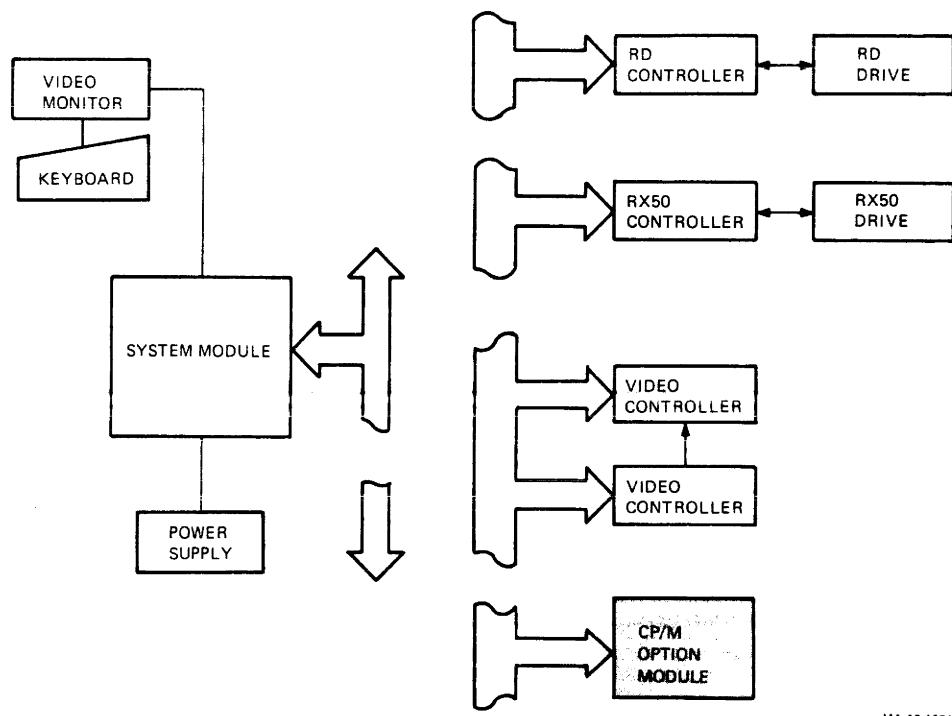

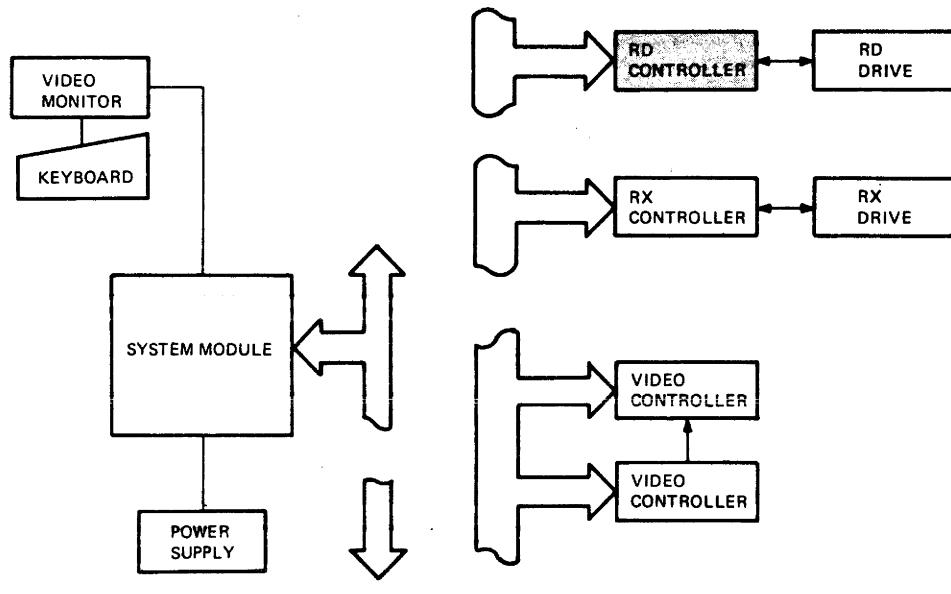

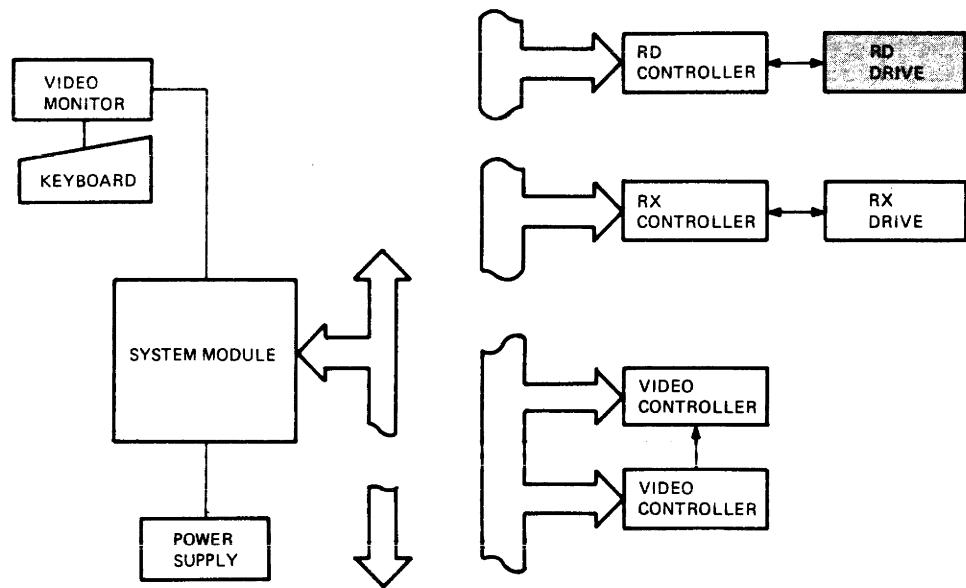

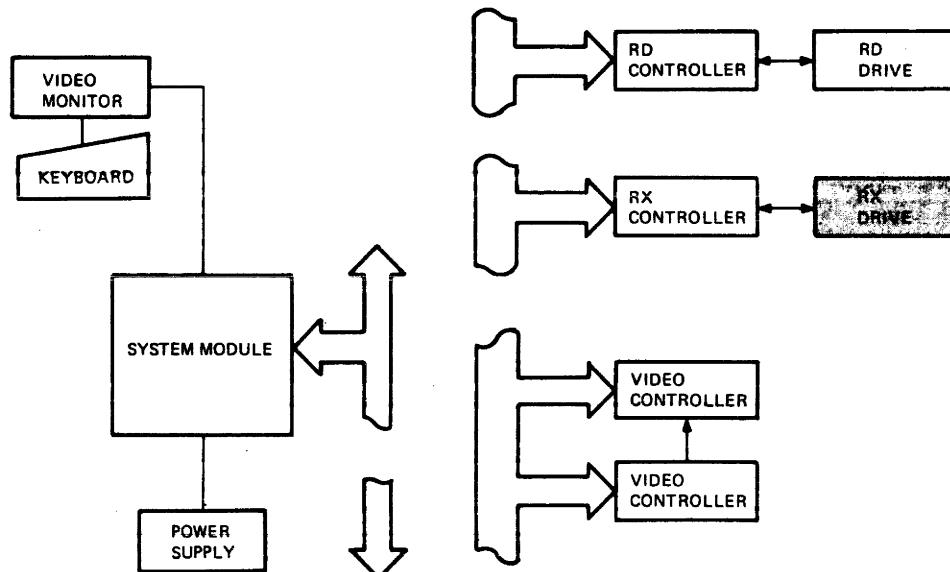

| 2-1  | Professional System Hardware Components .....                                                | 2-1  |

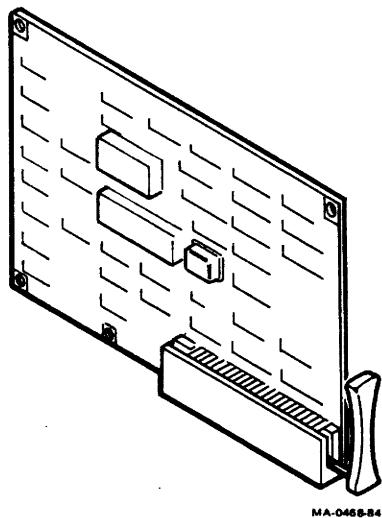

| 2-2  | CP/M Option Module .....                                                                     | 2-2  |

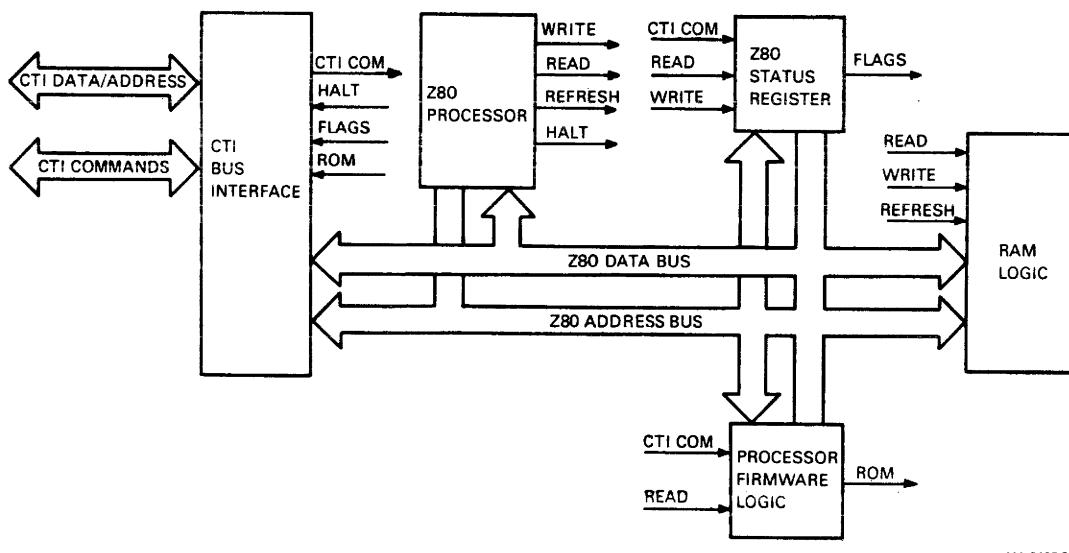

| 2-3  | Block Diagram .....                                                                          | 2-3  |

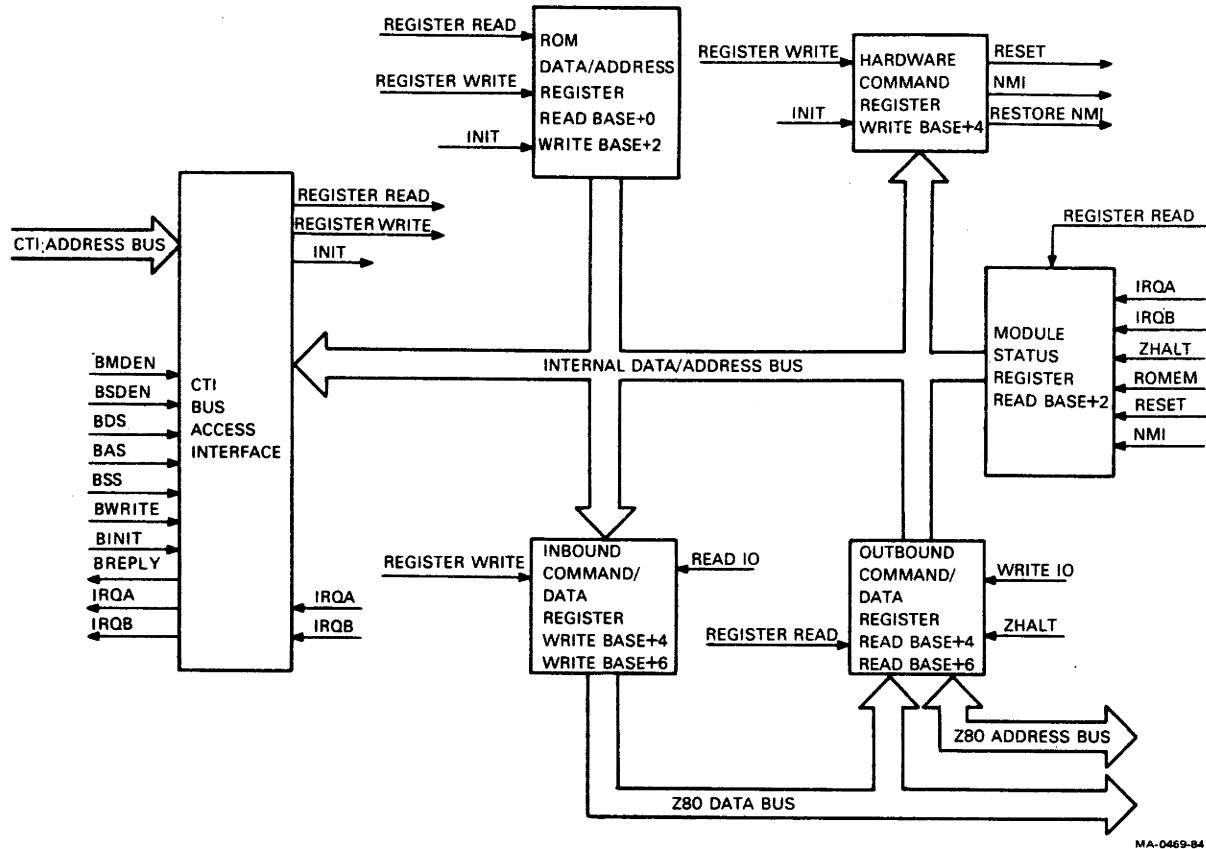

| 2-4  | CTI Bus Interface Circuits .....                                                             | 2-6  |

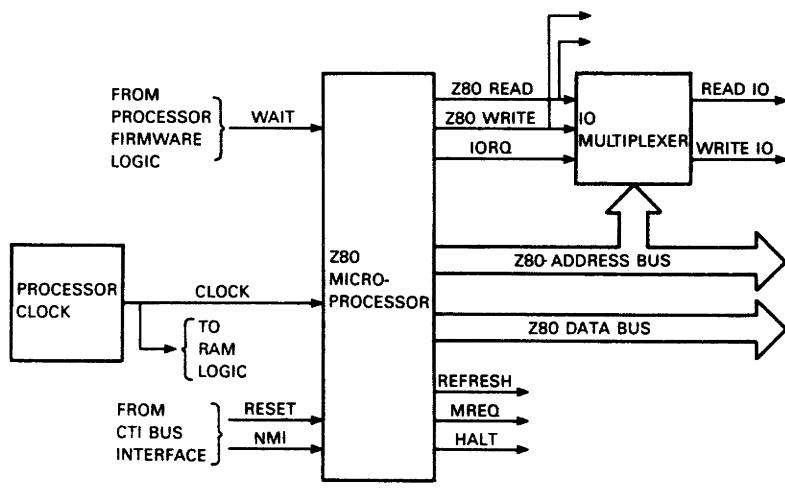

| 2-5  | Z80 Microprocessor Circuits .....                                                            | 2-8  |

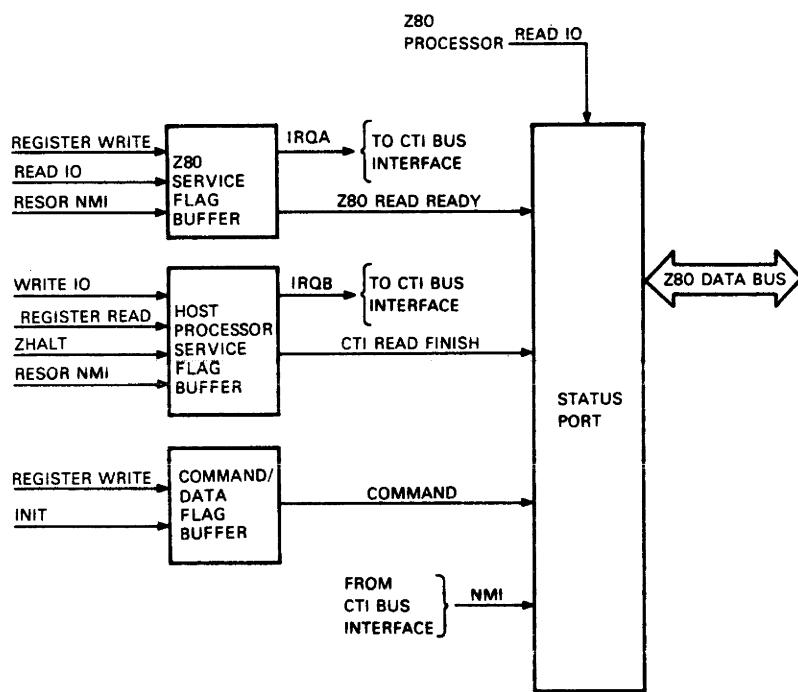

| 2-6  | Z80 Status Register Circuits .....                                                           | 2-9  |

| 2-7  | Z80 Microprocessor Firmware Logic .....                                                      | 2-11 |

| 2-8  | RAM Logic Circuits .....                                                                     | 2-12 |

| 2-9  | Status Register Bit Assignments .....                                                        | 2-16 |

| 3-1  | DECNA Option Module, Transceiver Cable 5 Loopback Connector .....                            | 3-1  |

| 3-2  | Ethernet Elements (Example) .....                                                            | 3-2  |

| 3-3  | Ethernet Frame Format .....                                                                  | 3-3  |

| 3-4  | DECNA Option Module Major Functional Block Diagram .....                                     | 3-4  |

| 3-5  | DECNA Ethernet Interface .....                                                               | 3-5  |

| 3-6  | CTI Bus Interface .....                                                                      | 3-7  |

| 3-7  | Bus Transceivers, Bus Command Registers, and Control Circuitry .....                         | 3-8  |

| 3-8  | Memory Access Register .....                                                                 | 3-11 |

| 3-9  | Control Register (Command Control Latch) .....                                               | 3-13 |

| 3-10 | Control Register Bit Values .....                                                            | 3-14 |

| 3-11 | Memory Read Base Address Register and Write-Only Latch, and<br>Base Address Comparator ..... | 3-16 |

| 3-12 | Dual-Ported Memory Base Address Register Bit Value .....                                     | 3-16 |

| 3-13 | Option ROM, Address ROM, and ROM Address Logic .....                                         | 3-18 |

| 3-14 | Dual-Ported Memory .....                                                                     | 3-20 |

| 3-15 | Dynamic RAM .....                                                                            | 3-21 |

| 3-16 | CTI Write/NI Write Selection .....                                                           | 3-22 |

|      |                                                               |      |

|------|---------------------------------------------------------------|------|

| 3-17 | Dual-Ported Memory Controller .....                           | 3-24 |

| 3-18 | CTI Read/Write Decoder .....                                  | 3-28 |

| 3-19 | Port A .....                                                  | 3-29 |

| 3-20 | Port B .....                                                  | 3-31 |

| 3-21 | Ethernet Interface .....                                      | 3-35 |

| 3-22 | Ethernet Controller .....                                     | 3-35 |

| 3-23 | Ethernet Serial Interface .....                               | 3-39 |

| 3-24 | Manchester Encoded Data .....                                 | 3-41 |

| 3-25 | Broadband Compatibility Circuit .....                         | 3-42 |

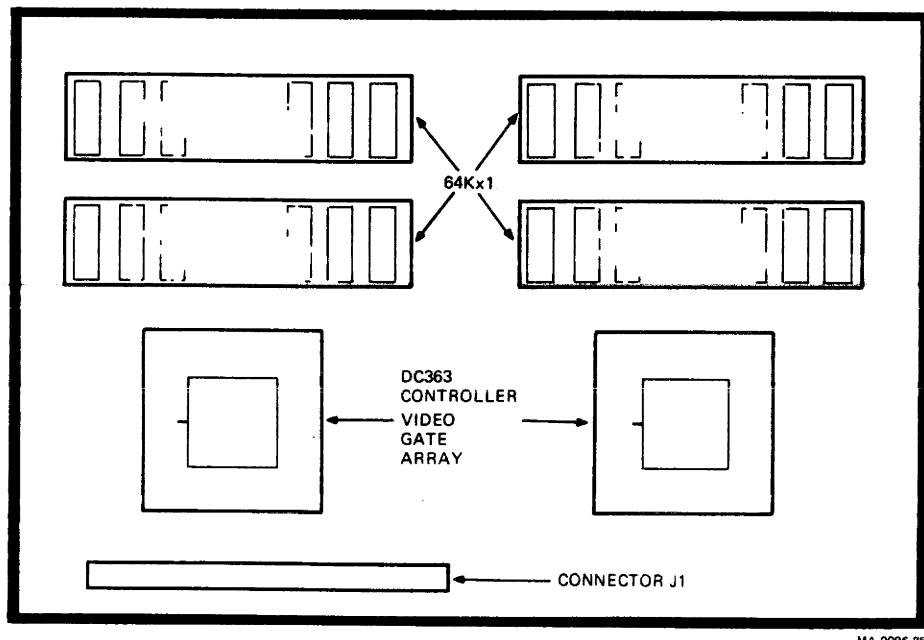

| 4-1  | Professional 380 EBO Physical Layout .....                    | 4-1  |

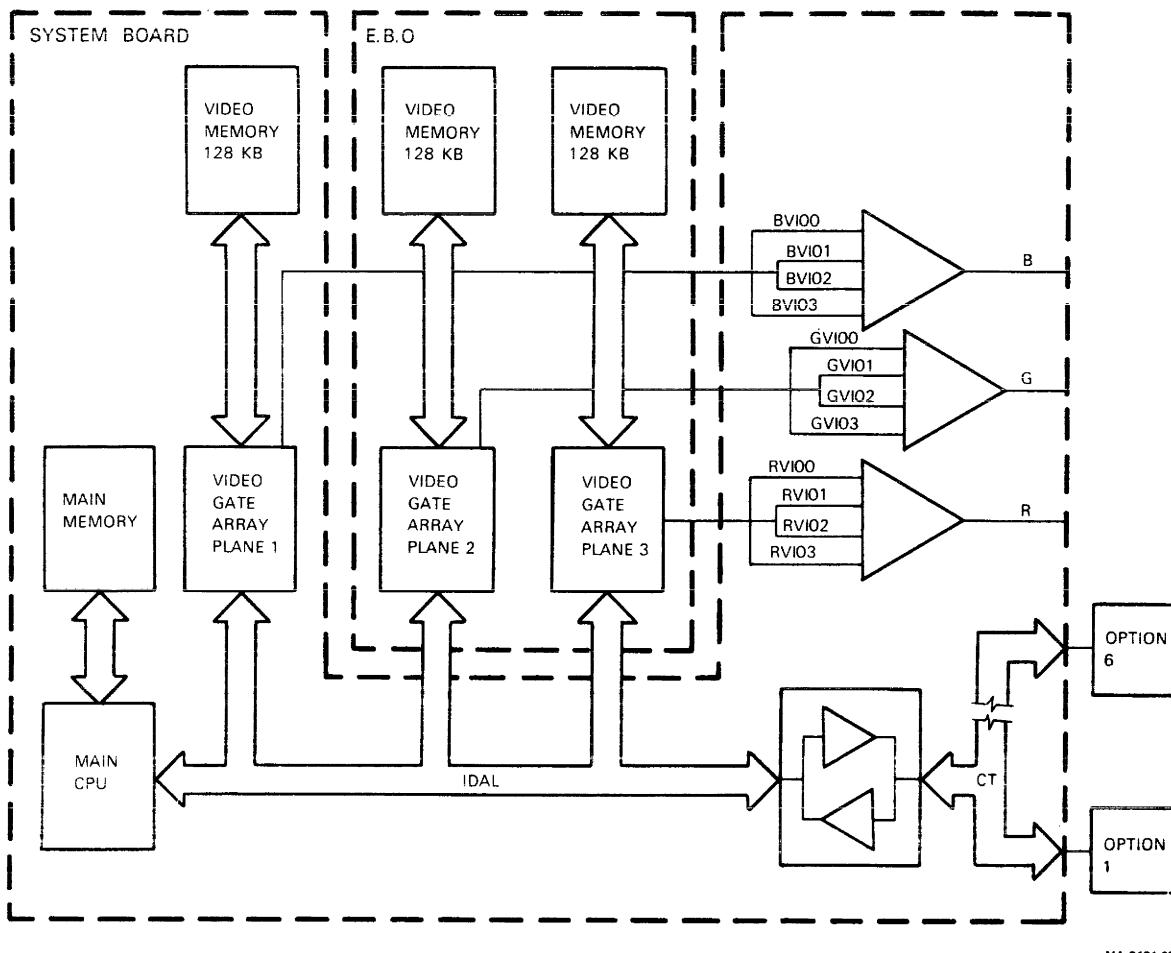

| 4-2  | Extended Bitmap Option Functional Block Diagram .....         | 4-3  |

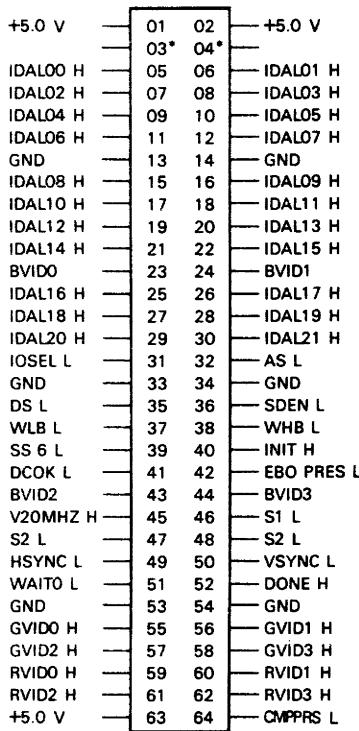

| 4-3  | Connector J1 Pin Assignment .....                             | 4-6  |

| 5-1  | Controller Module System Relation .....                       | 5-1  |

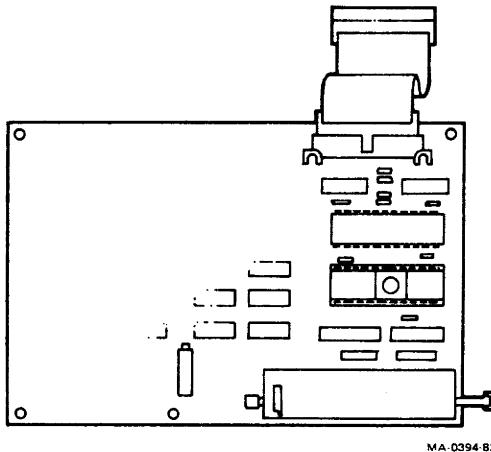

| 5-2  | Controller Module .....                                       | 5-2  |

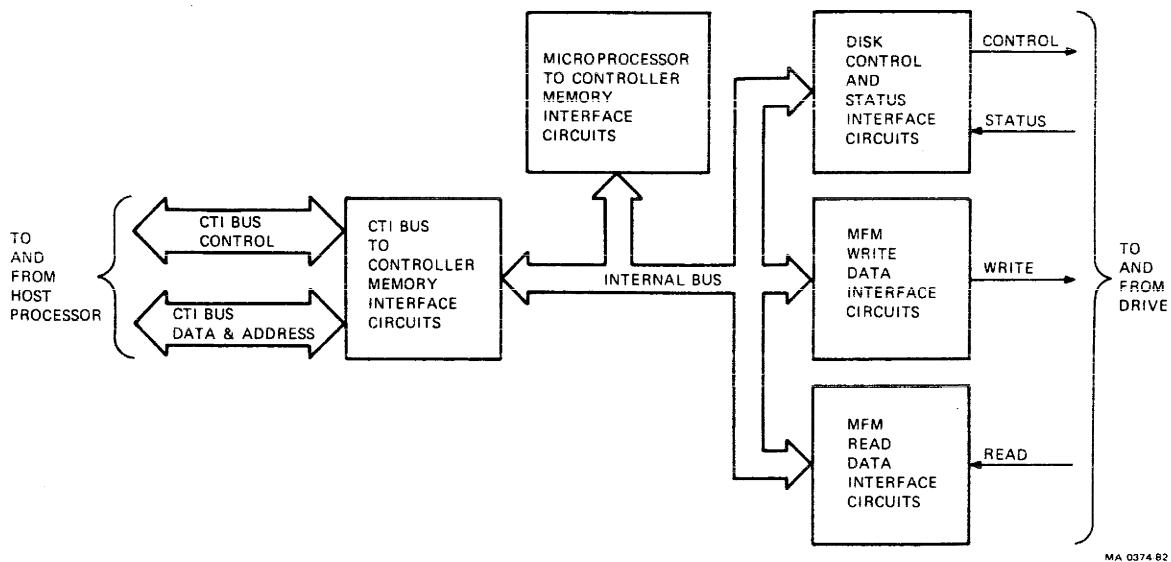

| 5-3  | Controller Module Block Diagram .....                         | 5-3  |

| 5-4  | CTI Bus Interface Circuits .....                              | 5-7  |

| 5-5  | Microprocessor ( $\mu$ P) Control Circuits .....              | 5-9  |

| 5-6  | Disk Control and Status Circuits .....                        | 5-10 |

| 5-7  | Modified Frequency Modulation (MFM) Write Data Circuits ..... | 5-11 |

| 5-8  | MFM Read Data Circuits .....                                  | 5-13 |

| 5-9  | Controller Module Data Flow Diagram .....                     | 5-15 |

| 5-10 | Controller Module Interface Signal Flow .....                 | 5-16 |

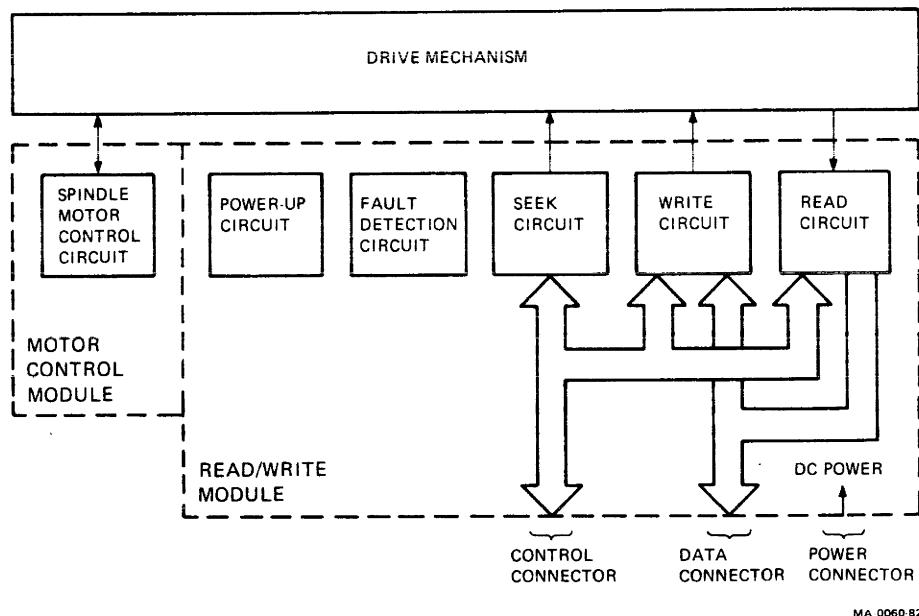

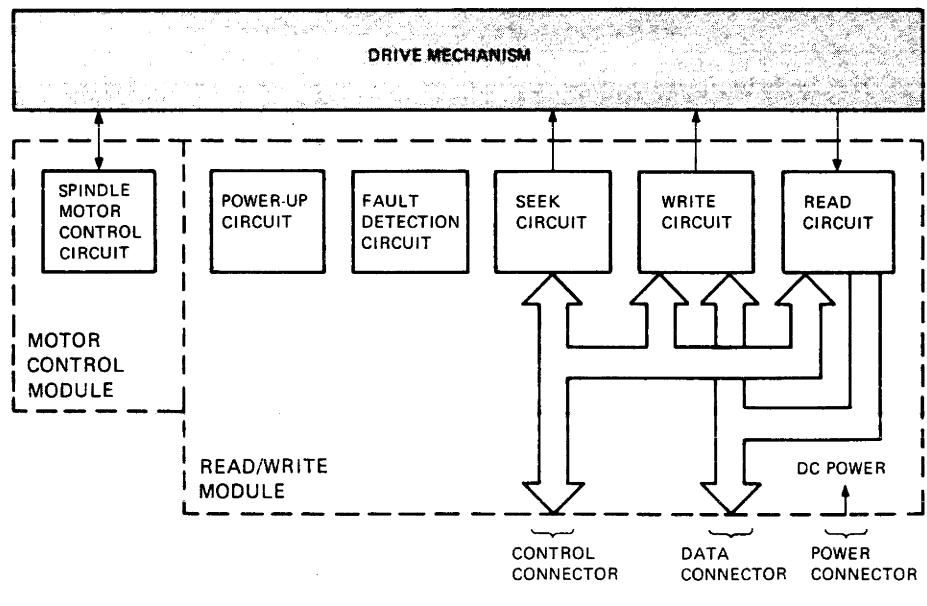

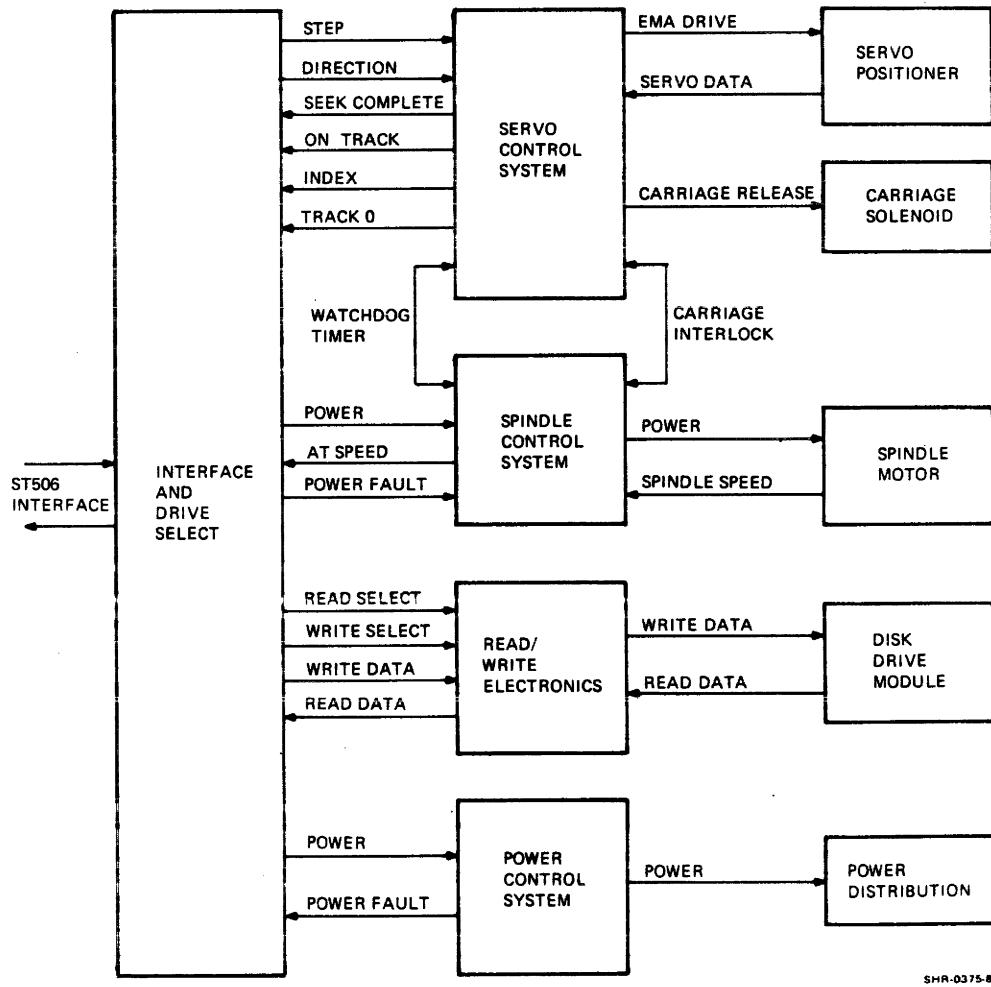

| 6-1  | Hard Disk Drive System Relation .....                         | 6-1  |

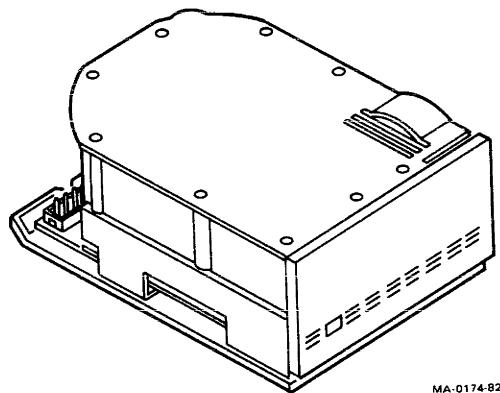

| 6-2  | Hard Disk Drive .....                                         | 6-3  |

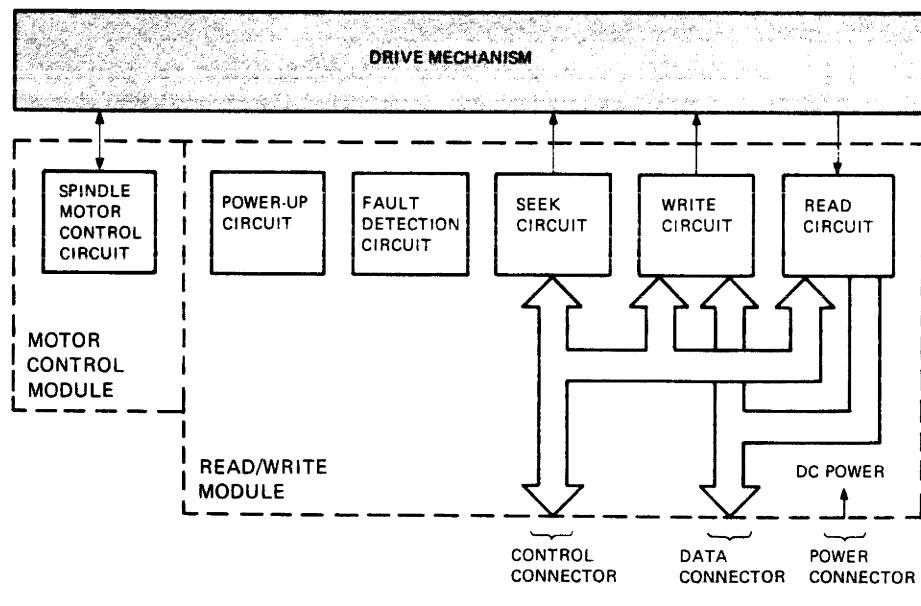

| 6-3  | Simple Block Diagram .....                                    | 6-3  |

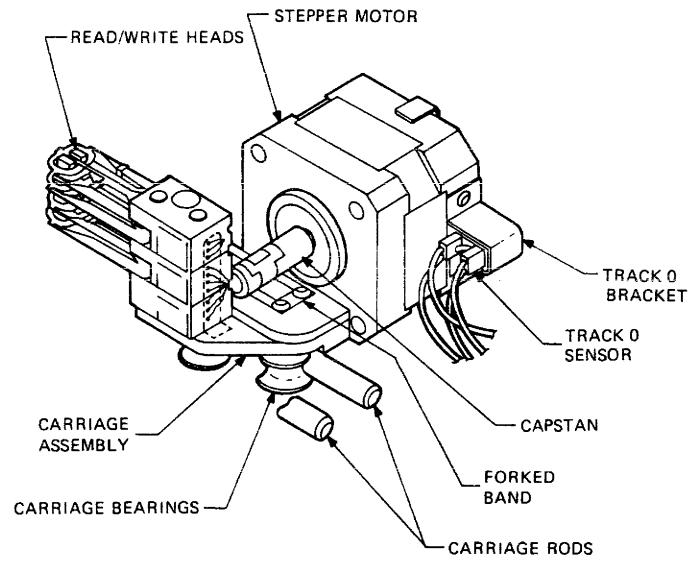

| 6-4  | Stepper Motor and Head Carriage Assembly .....                | 6-5  |

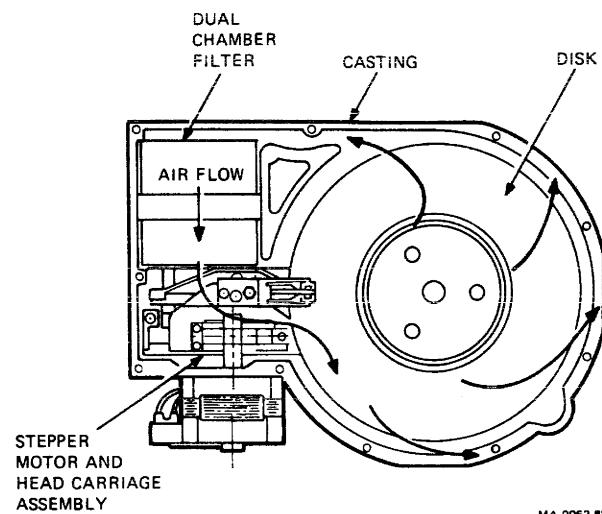

| 6-5  | Air Flow Top View .....                                       | 6-7  |

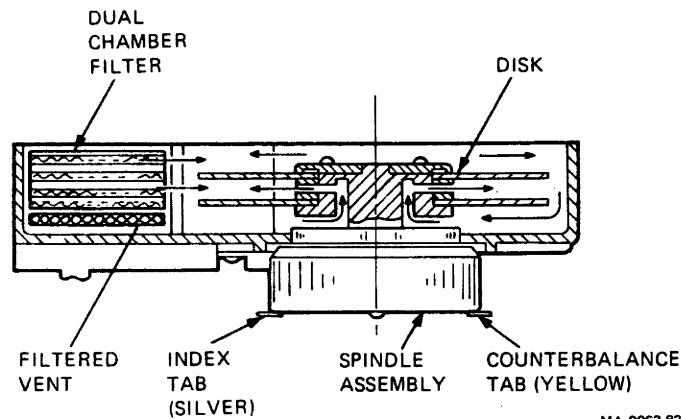

| 6-6  | Air Flow Side View .....                                      | 6-8  |

| 6-7  | Spindle Motor Control Circuit Detail .....                    | 6-11 |

| 6-8  | Power-up Circuit Detail .....                                 | 6-13 |

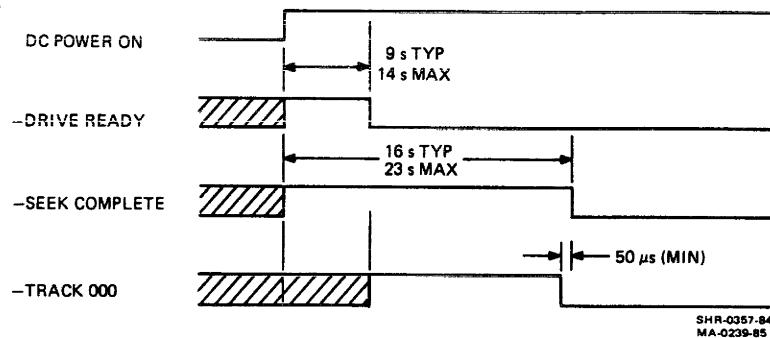

| 6-9  | Power-up Sequence Timing .....                                | 6-14 |

| 6-10 | Fault Detection Circuit Detail .....                          | 6-15 |

| 6-11 | Seek Circuit Detail .....                                     | 6-17 |

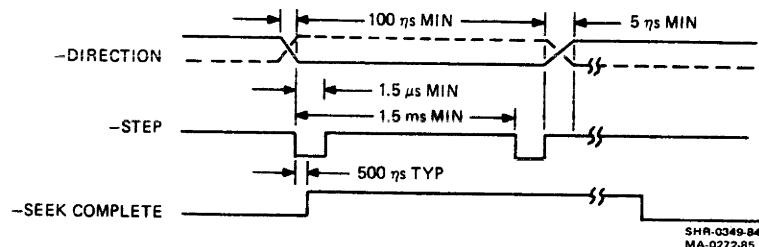

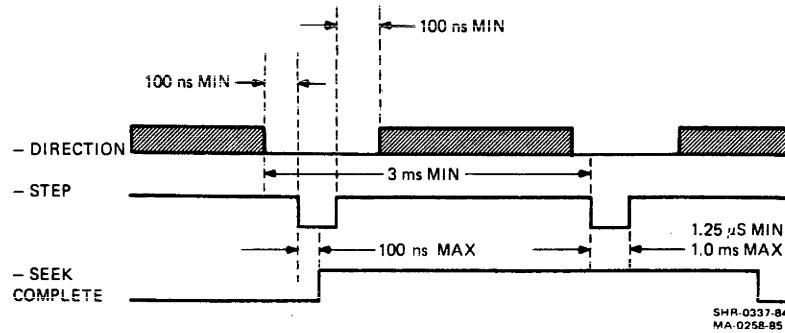

| 6-12 | Seek Circuit Timing .....                                     | 6-19 |

| 6-13 | Write Circuit Detail .....                                    | 6-20 |

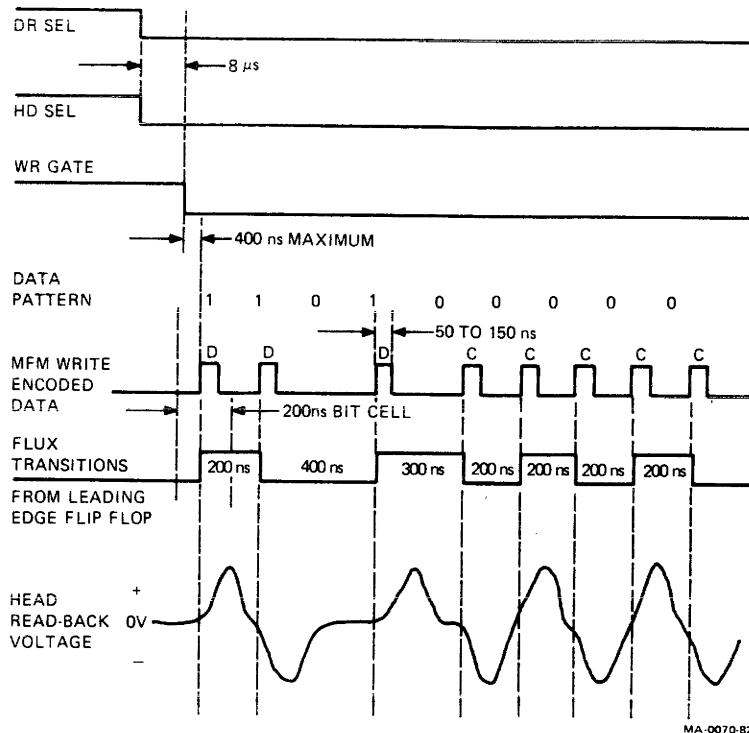

| 6-14 | Write Data Timing .....                                       | 6-21 |

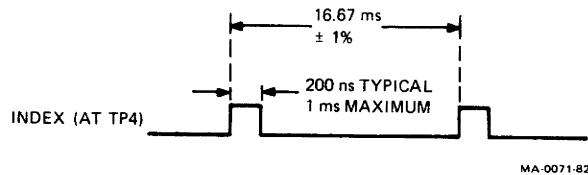

| 6-15 | Index Signal Timing .....                                     | 6-21 |

| 6-16 | Read Circuit Detail .....                                     | 6-22 |

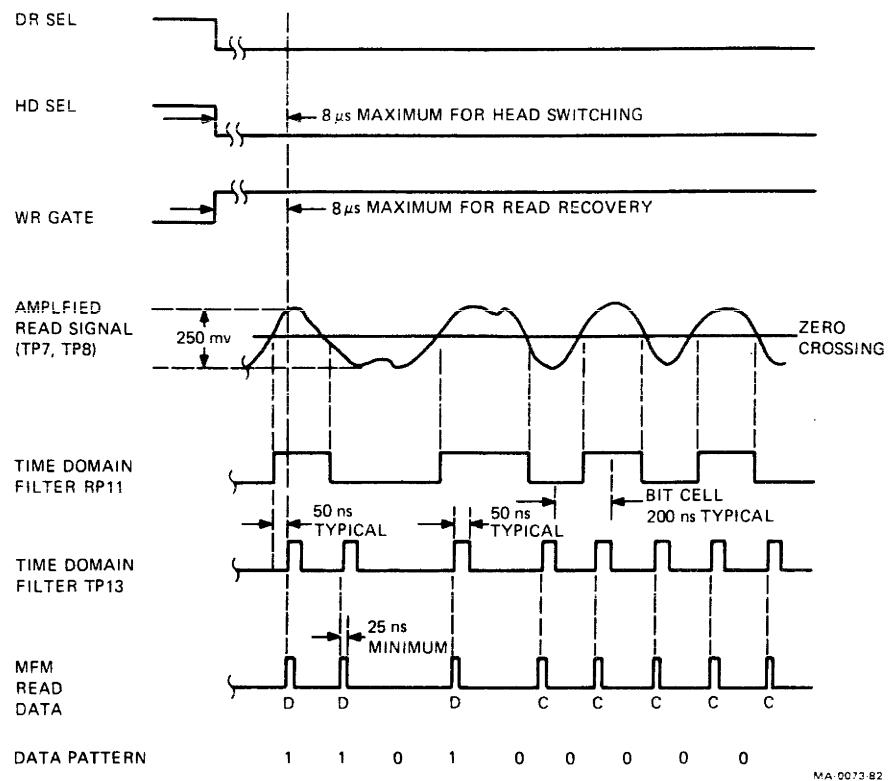

| 6-17 | Read Data Timing .....                                        | 6-23 |

| 6-18 | Interface Signal Connections .....                            | 6-24 |

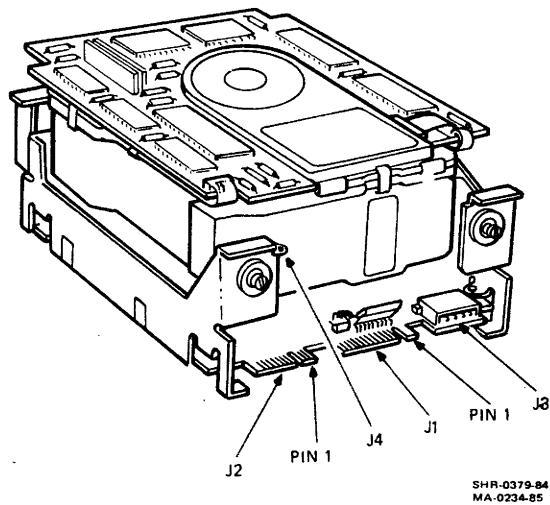

| 6-19 | I/O Connector Locations .....                                 | 6-25 |

| 6-20 | Internal Connection Locations .....                           | 6-28 |

| 6-21 | Read/Write Module Test Point Locations .....                  | 6-31 |

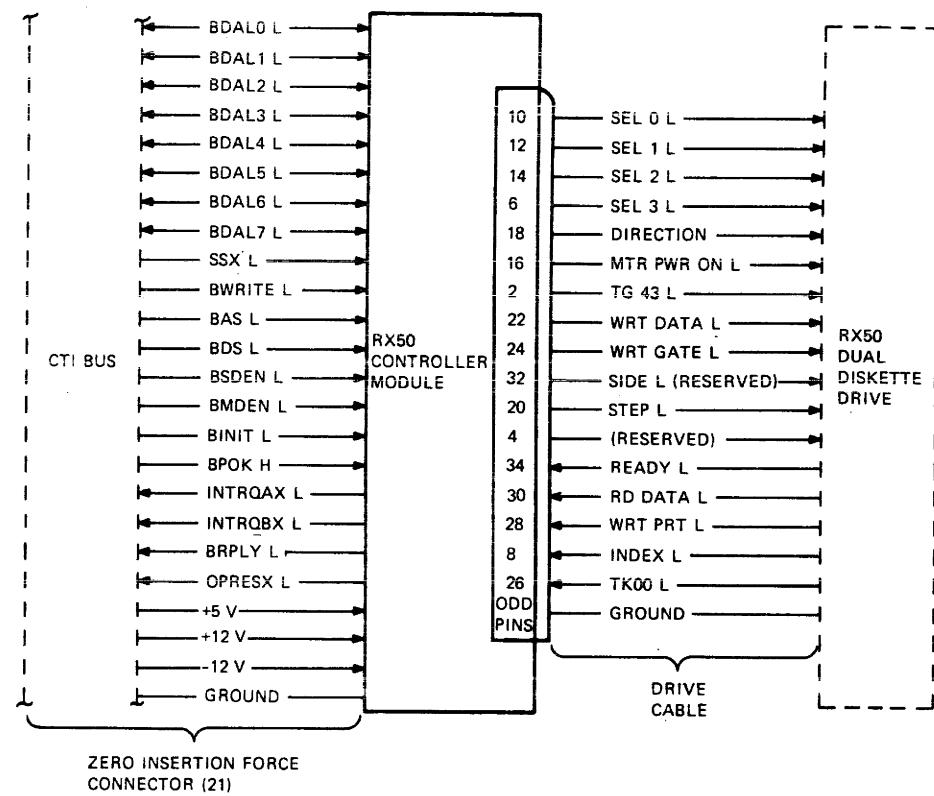

| 7-1  | RX50 Controller Module System Relation .....                  | 7-1  |

| 7-2  | RX50 Controller Module .....                                  | 7-2  |

| 7-3  | RX50 Controller Module Block Diagram .....                    | 7-3  |

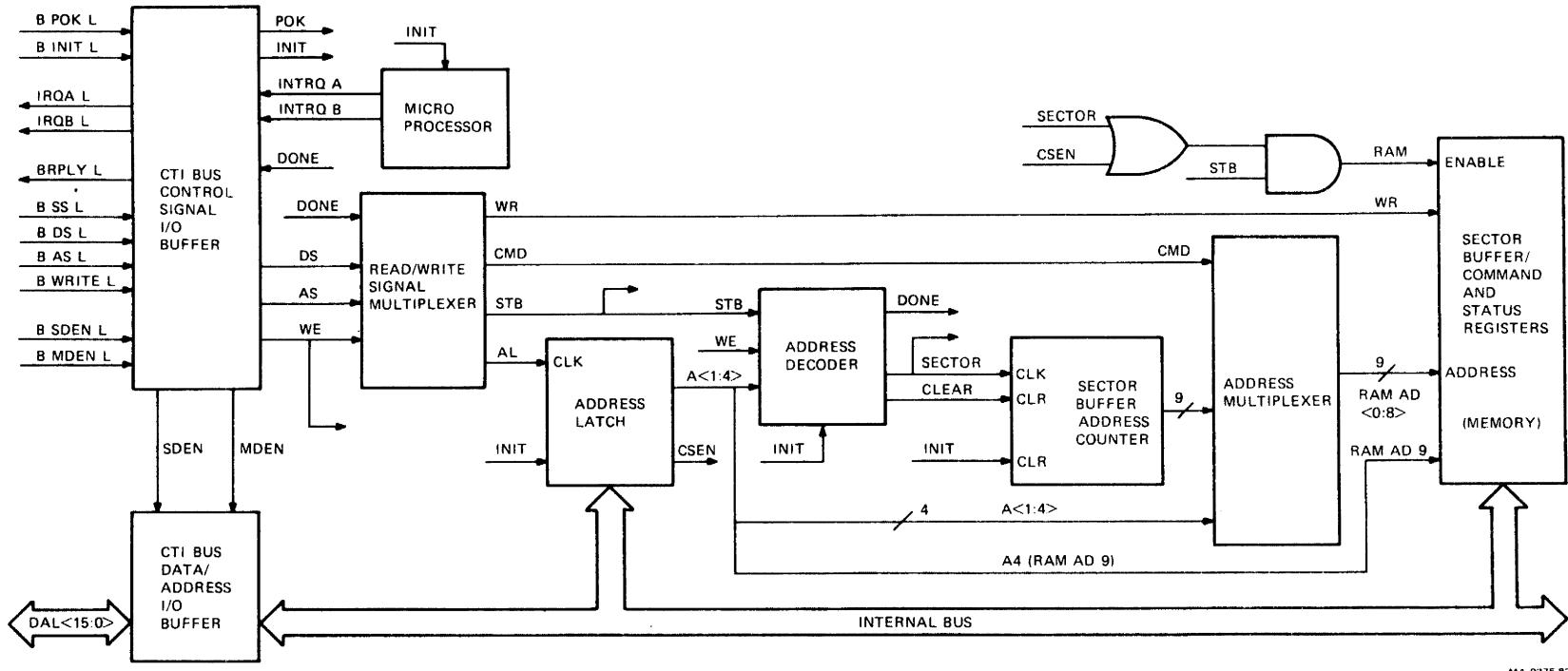

| 7-4  | CTI Bus to Controller Memory Interface Circuits .....         | 7-6  |

| 7-5  | Microprocessor to Controller Memory Interface Circuits .....  | 7-11 |

| 7-6  | Disk Control and Status Interface Circuits .....              | 7-13 |

|      |                                                               |      |

|------|---------------------------------------------------------------|------|

| 7-7  | MFM Write Data Interface Circuits .....                       | 7-16 |

| 7-8  | MFM Read Data Interface Circuits .....                        | 7-18 |

| 7-9  | RX50 Controller Module Interface Signal Flow .....            | 7-21 |

| 7-10 | RX5CS0 Command Mode Bit Definitions .....                     | 7-25 |

| 7-11 | RX5CS0 Maintenance Status Mode Bit Definitions .....          | 7-27 |

| 7-12 | RX5CS1 Command Mode Bit Definitions .....                     | 7-28 |

| 7-13 | RX5CS2 Command Mode Bit Definitions .....                     | 7-30 |

| 7-14 | RX5CS2 Extended Function Mode Bit Definitions .....           | 7-31 |

| 7-15 | RX5CS3 Maintenance Mode Status Bit Definitions .....          | 7-32 |

| 7-16 | RX5CS3 Extended Functions Mode Bit Definitions (Report) ..... | 7-33 |

| 7-17 | RX5CS3 Extended Functions Mode Bit Definition (Set) .....     | 7-33 |

| 7-18 | RX5CS4 Maintenance Status Mode Bit Definition .....           | 7-34 |

| 7-19 | RX5CS4 Read/Write Status Mode Bit Definition .....            | 7-34 |

| 7-20 | RX5CS4 Extended Functions Mode Bit Definition .....           | 7-35 |

| 7-21 | RX5CS5 Bit Definitions .....                                  | 7-35 |

| 7-22 | RX5CS5 Selectable Extended Functions .....                    | 7-35 |

| 7-23 | RX5EB Bit Definition .....                                    | 7-37 |

| 7-24 | RX5FB Bit Definition .....                                    | 7-38 |

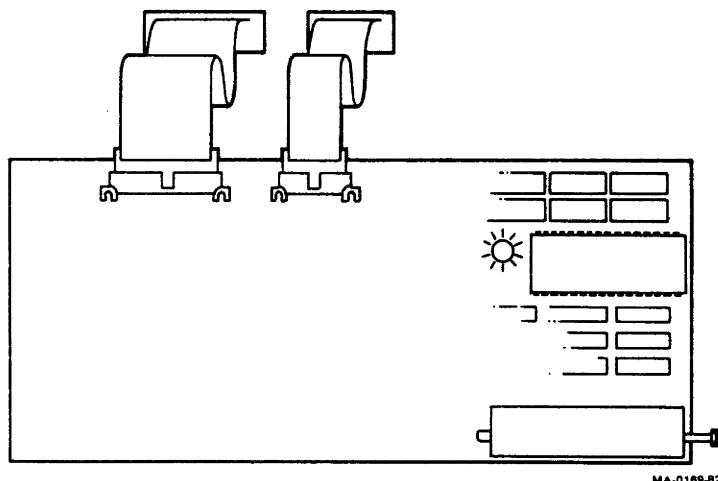

| 8-1  | RX50 Dual Diskette System Relation .....                      | 8-1  |

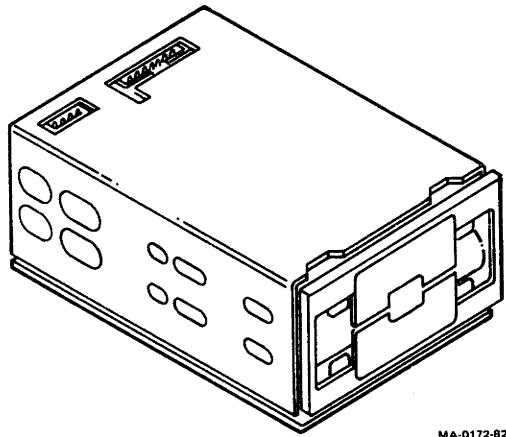

| 8-2  | RX50 Dual Diskette Drive .....                                | 8-2  |

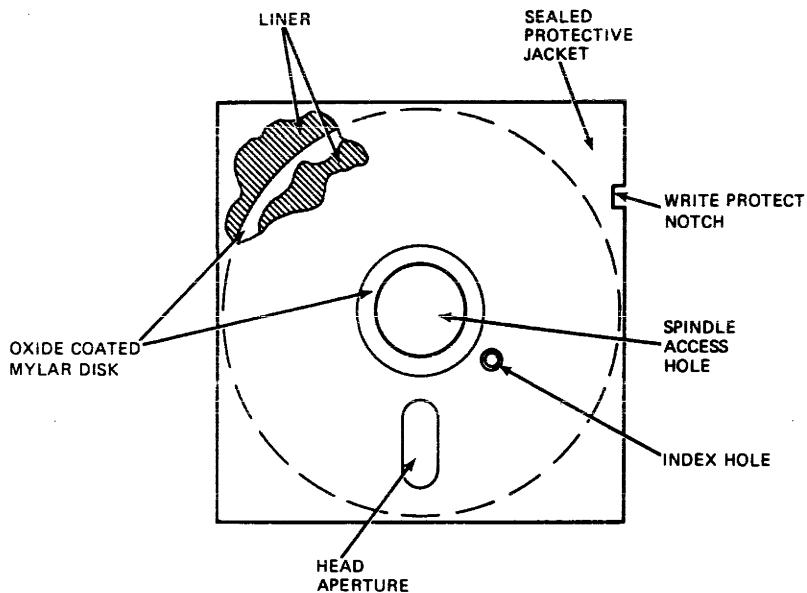

| 8-3  | The 5.25-inch Diskette .....                                  | 8-3  |

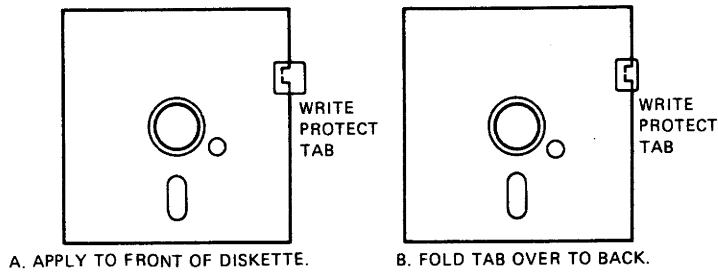

| 8-4  | Write Protect Tab Application .....                           | 8-4  |

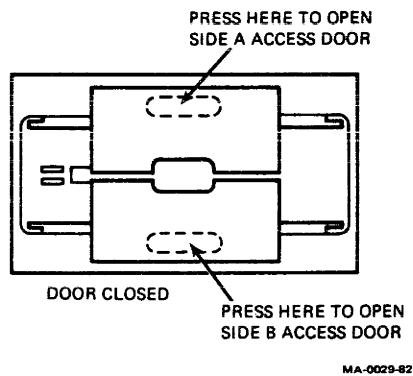

| 8-5  | Opening Access Doors .....                                    | 8-5  |

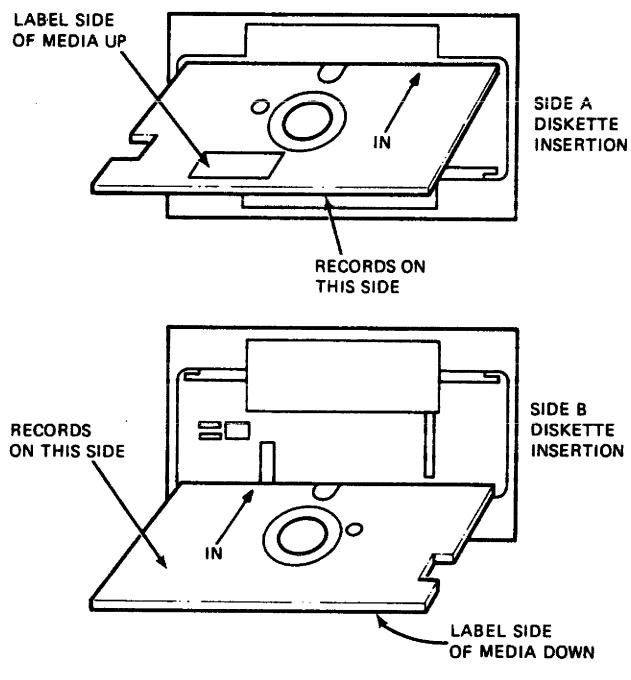

| 8-6  | Inserting Diskette .....                                      | 8-5  |

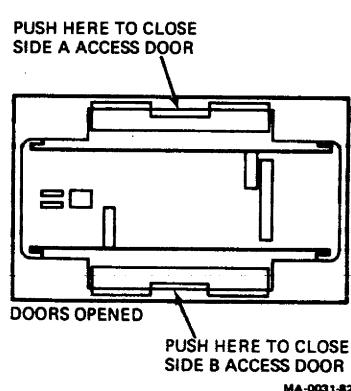

| 8-7  | Closing Access Doors .....                                    | 8-5  |

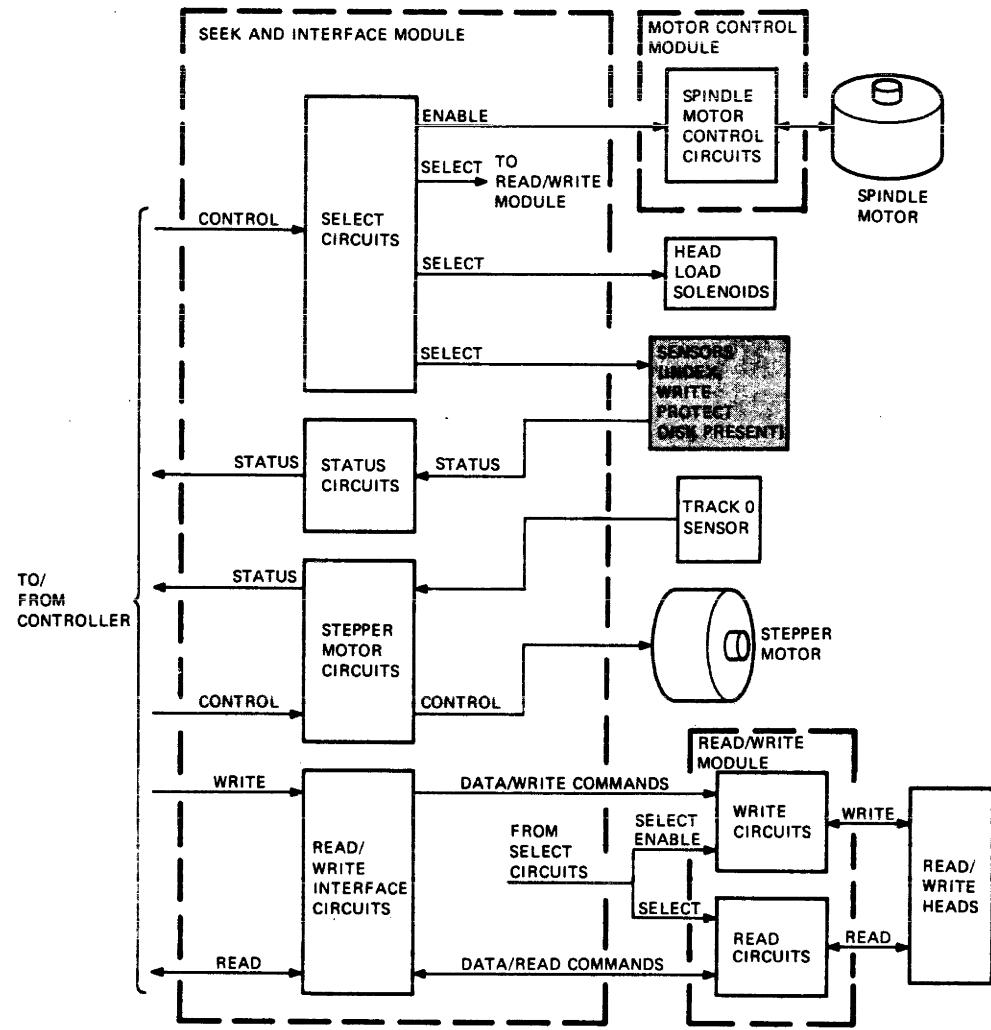

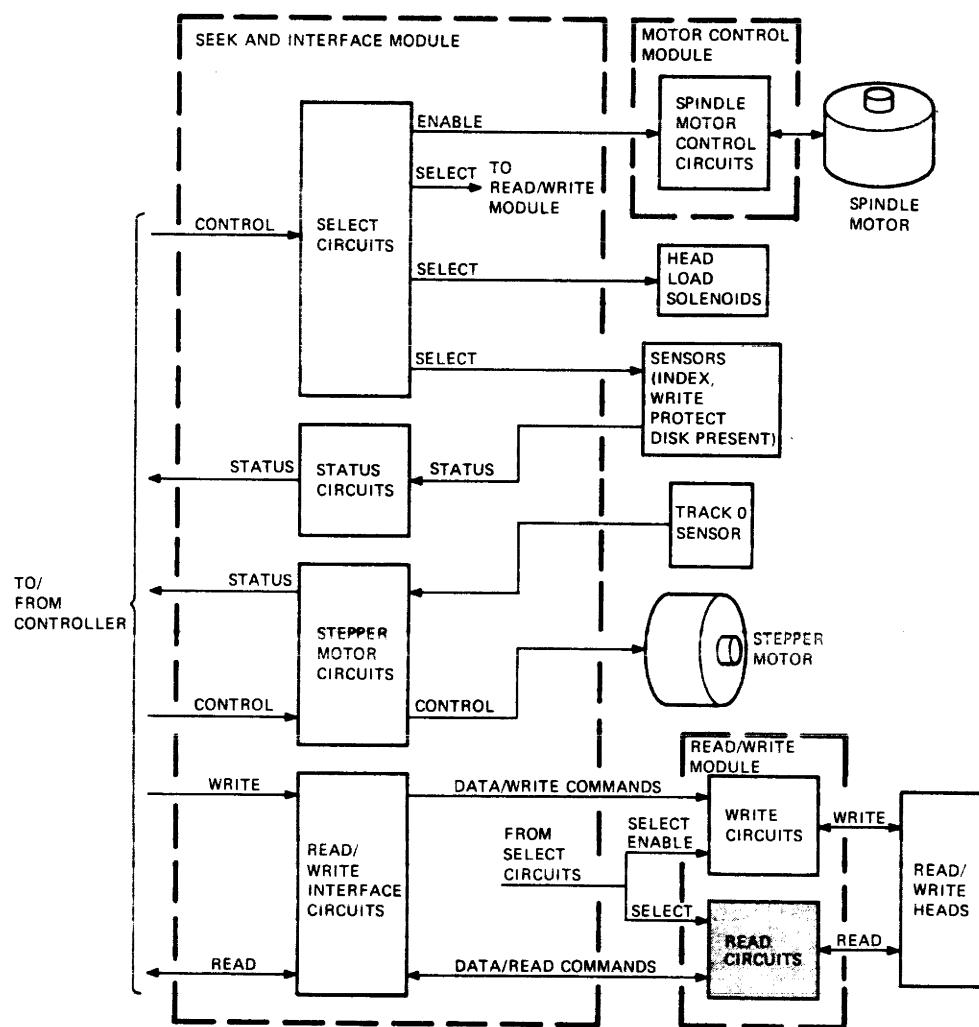

| 8-8  | Simple Block Diagram .....                                    | 8-7  |

| 8-9  | Mechanical Detail .....                                       | 8-9  |

| 8-10 | Mechanical Operation .....                                    | 8-10 |

| 8-11 | Select Circuit .....                                          | 8-15 |

| 8-12 | Motor Control Circuit .....                                   | 8-17 |

| 8-13 | Motor Control Wave Forms .....                                | 8-18 |

| 8-14 | Connections to Head Load Solenoids and Indicators .....       | 8-21 |

| 8-15 | Status Circuit .....                                          | 8-22 |

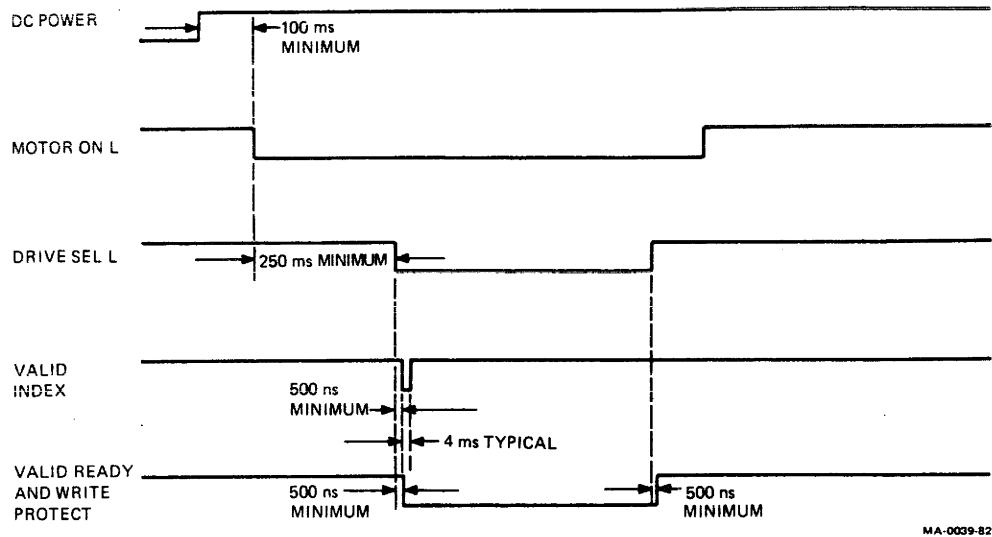

| 8-16 | Status Circuit Timing Relationships .....                     | 8-23 |

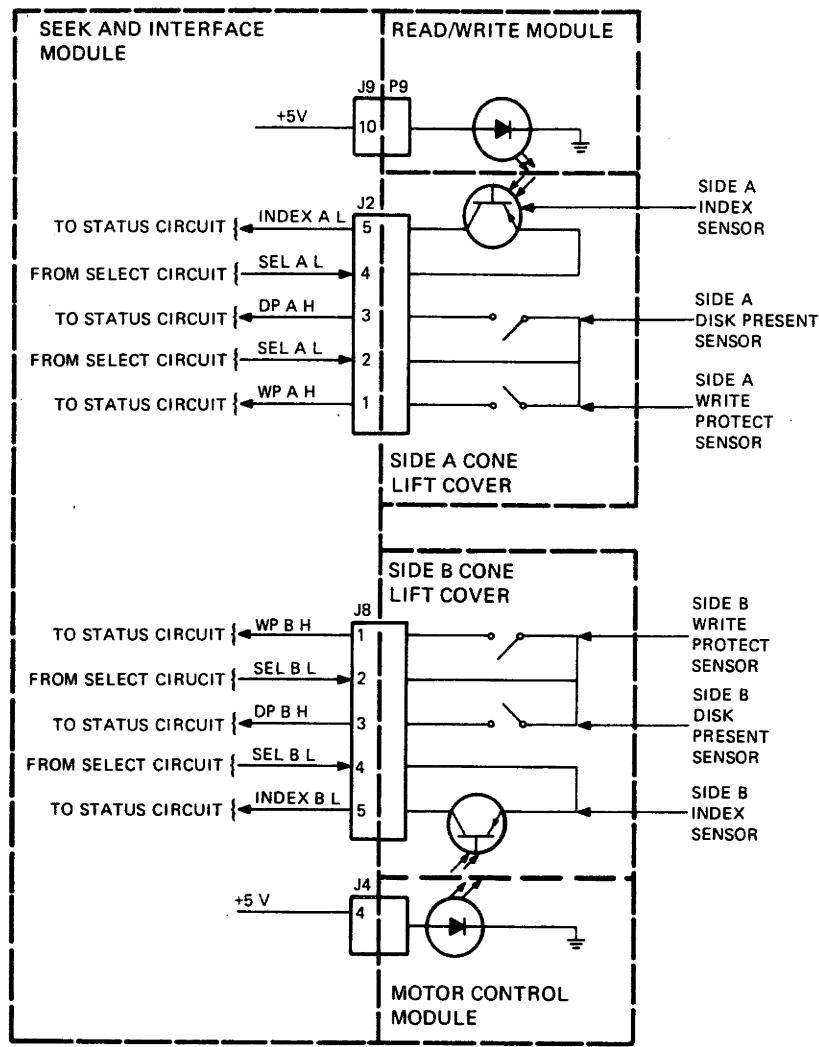

| 8-17 | Sensor .....                                                  | 8-24 |

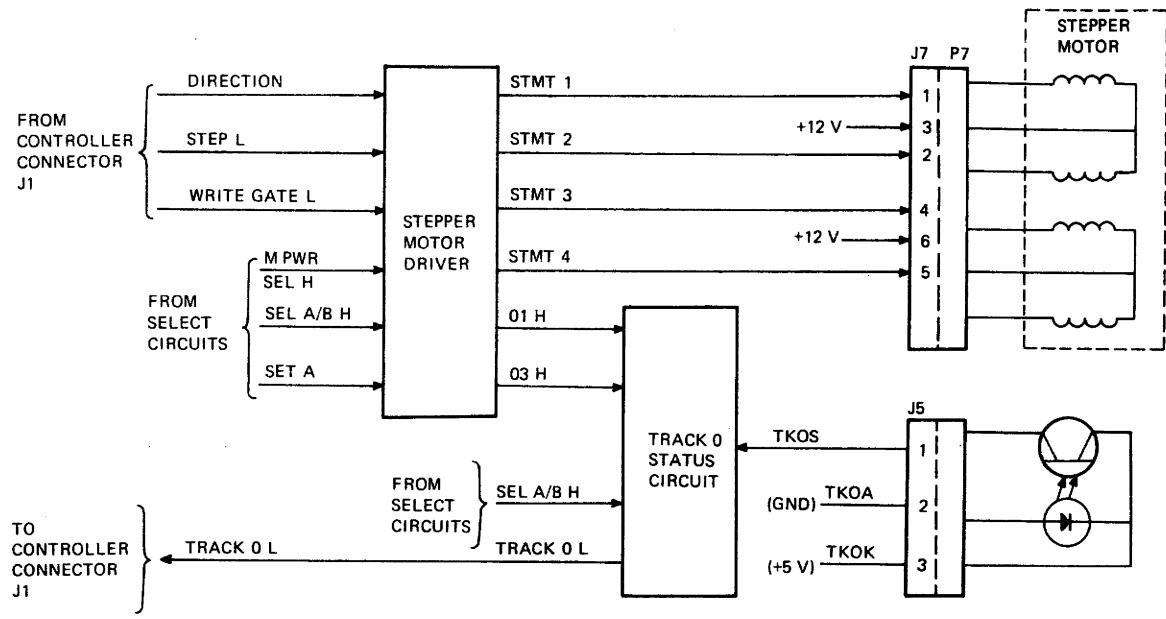

| 8-18 | Stepper Motor Circuit .....                                   | 8-26 |

| 8-19 | Stepper Motor Timing Relationships .....                      | 8-27 |

| 8-20 | Read/Write Interface Circuit .....                            | 8-29 |

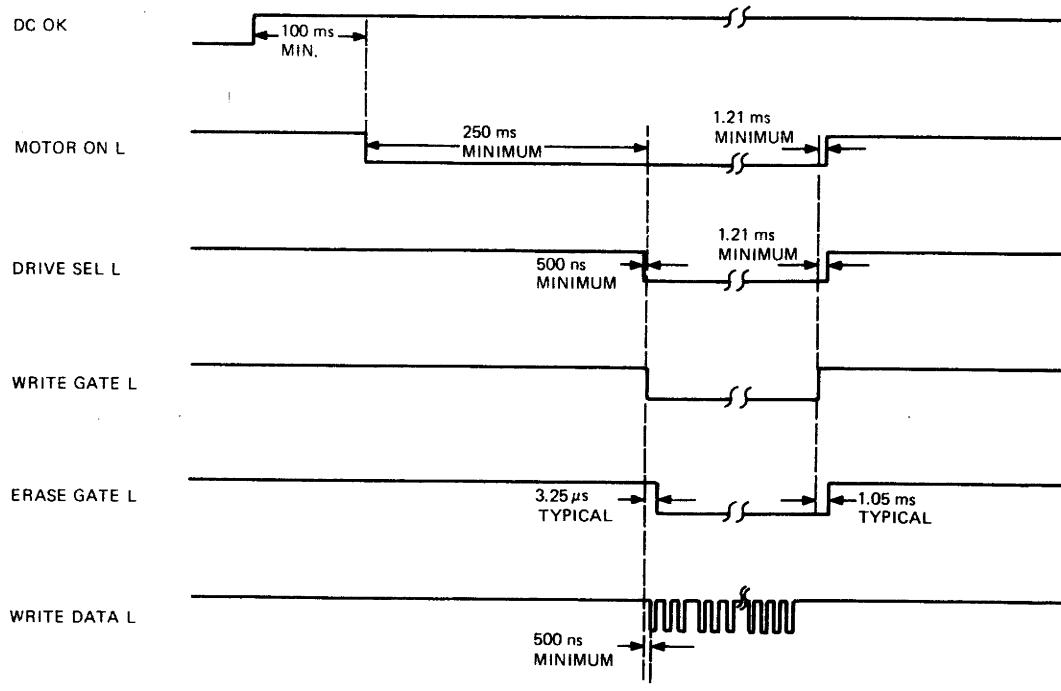

| 8-21 | Write Data Timing Relationships .....                         | 8-30 |

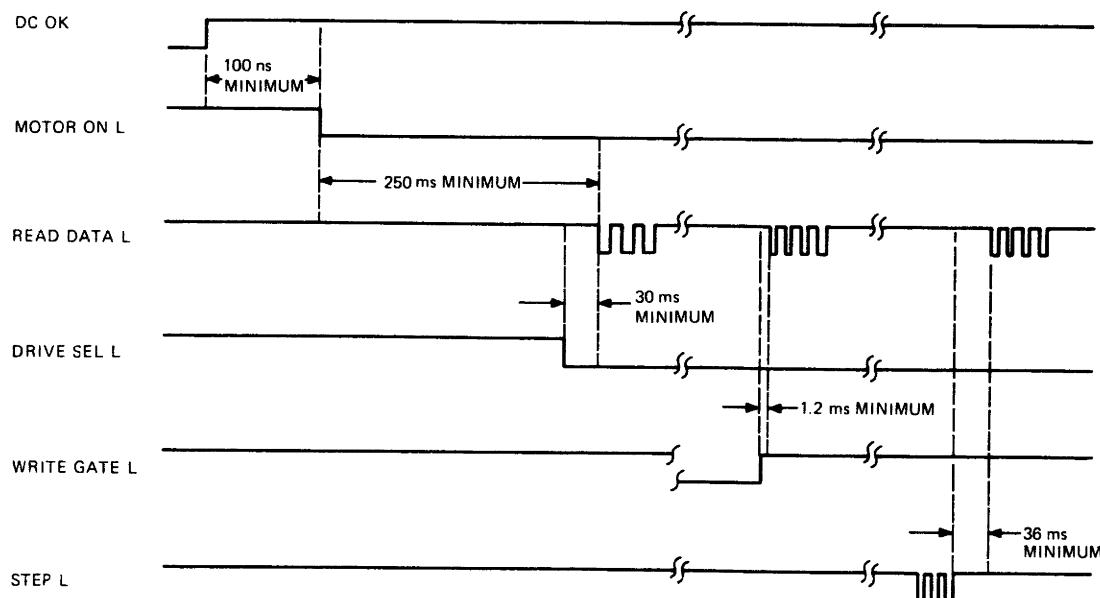

| 8-22 | Read Data Timing Relationships .....                          | 8-30 |

| 8-23 | Write Circuit .....                                           | 8-31 |

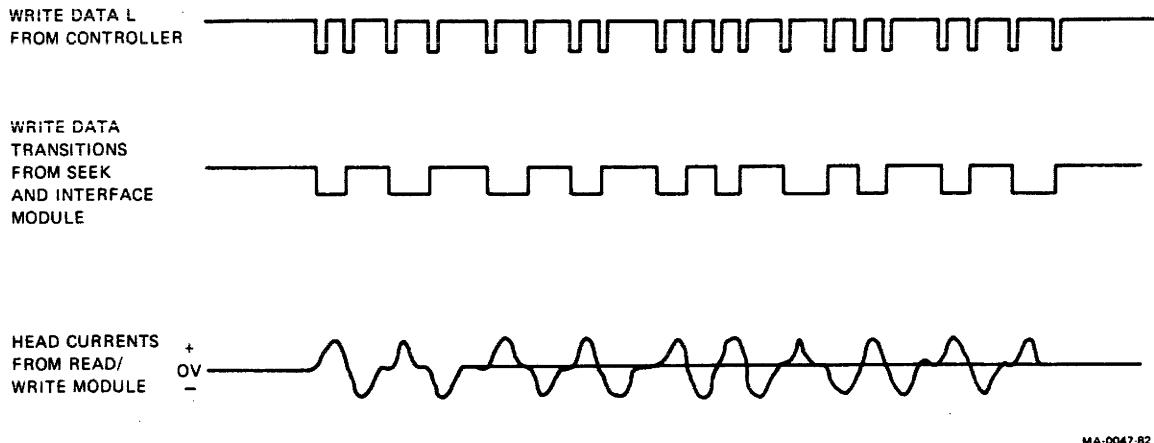

| 8-24 | Write Data to Head Current Conversion .....                   | 8-33 |

| 8-25 | Read Circuit .....                                            | 8-35 |

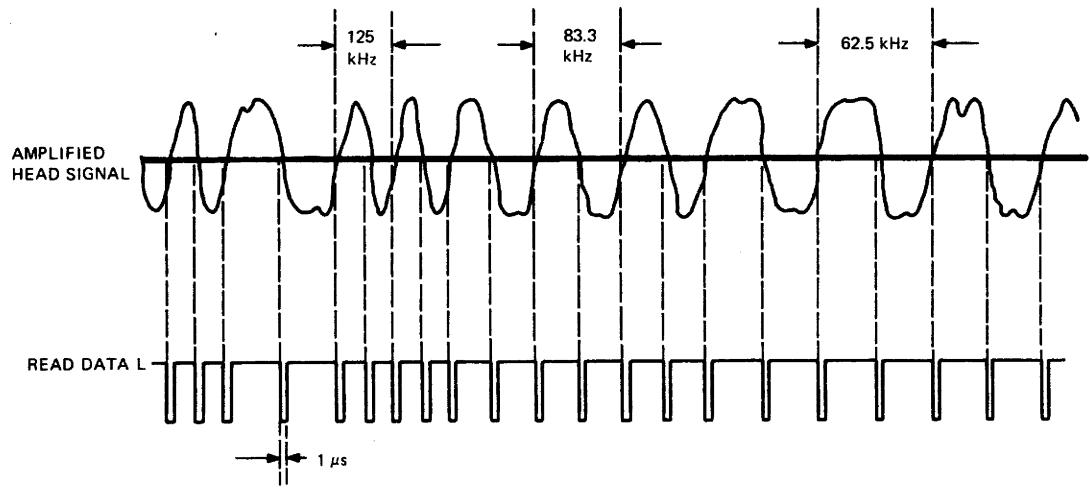

| 8-26 | Head Signal to Read Data Conversion .....                     | 8-36 |

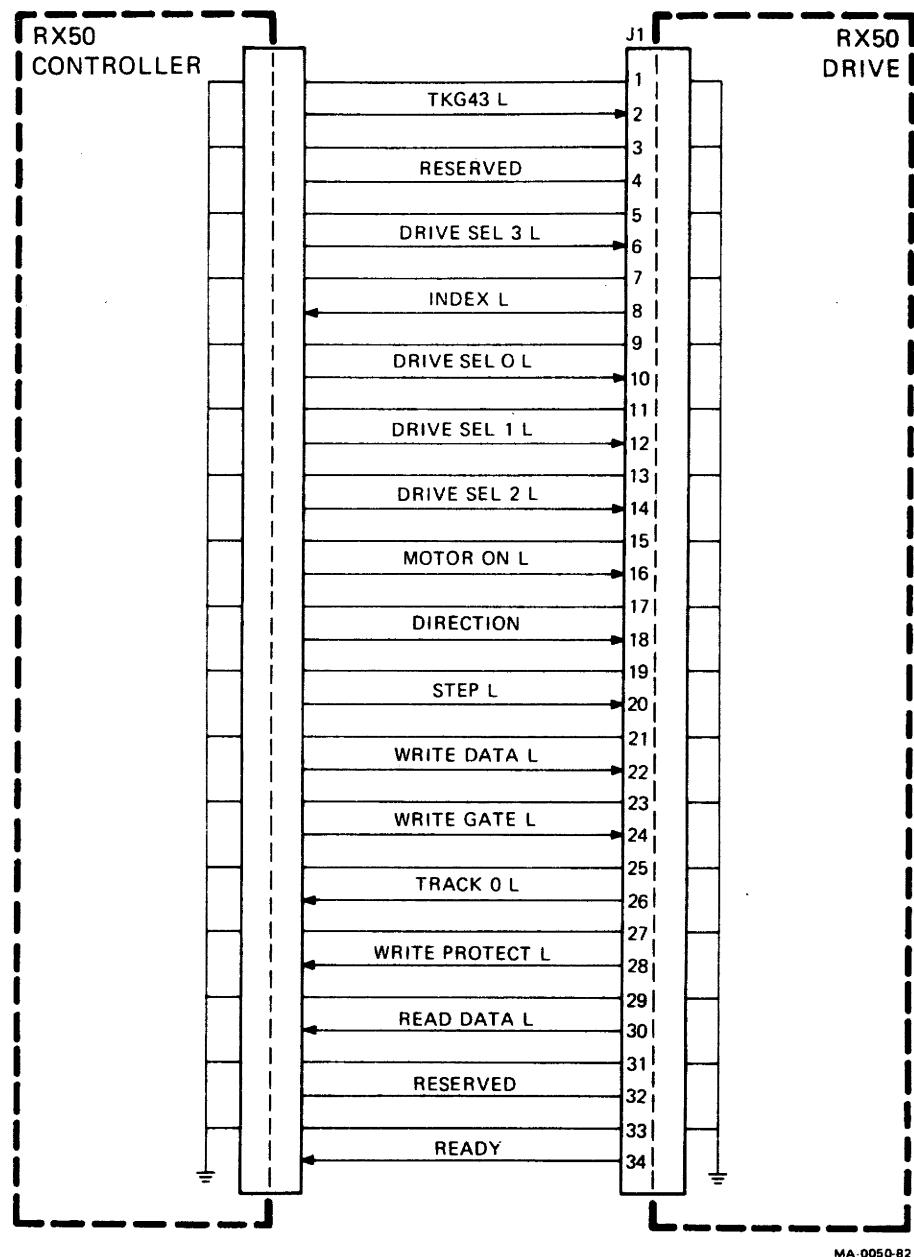

| 8-27 | RX50 Controller Module and Drive Interface Signal Flow .....  | 8-38 |

| 8-28 | Seek and Interface Module Connector Locations .....           | 8-39 |

| 8-29 | Motor Control Module Connector Locations .....                | 8-43 |

| 8-30 | Read/Write Module Connector Locations .....                   | 8-44 |

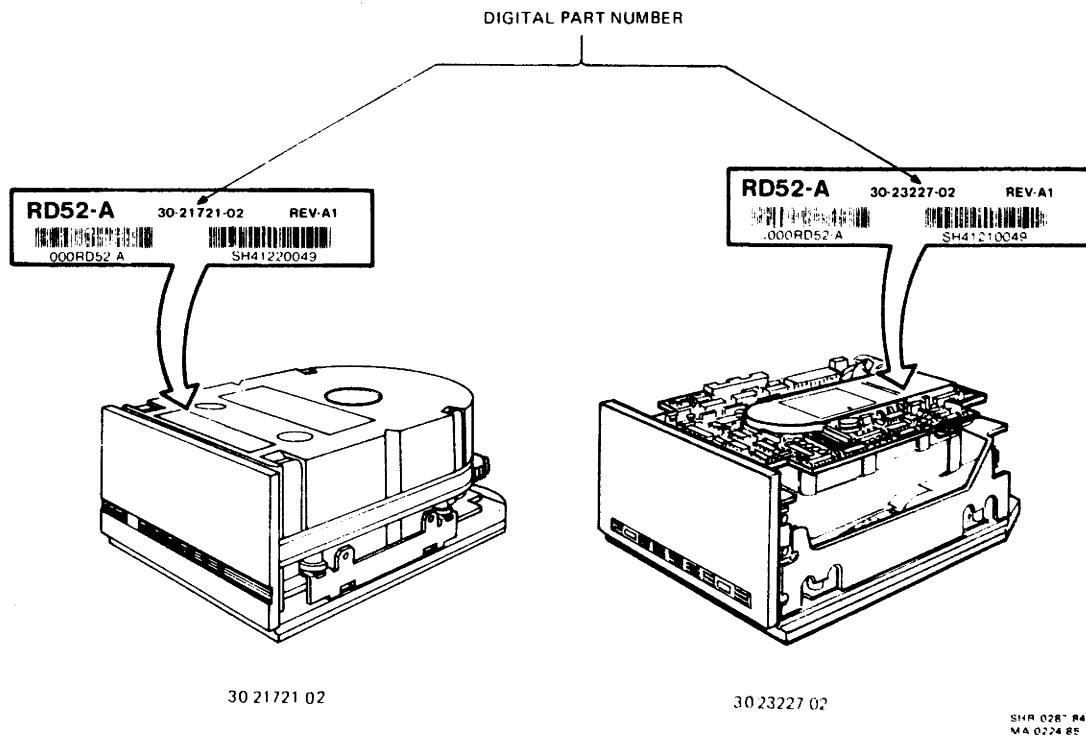

| 9-1  | RD52-A ID Label Location .....                                | 9-2  |

|      |                                           |      |

|------|-------------------------------------------|------|

| 9-2  | RD52-A Part Number Location .....         | 9-2  |

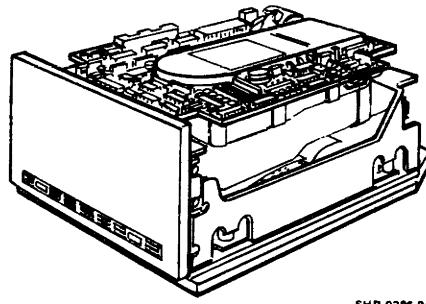

| 9-3  | RD52-A Disk Drive .....                   | 9-4  |

| 9-4  | Drive Startup Current Profile .....       | 9-6  |

| 9-5  | J3 Connector .....                        | 9-7  |

| 9-6  | RD52-A Mechanical Layout .....            | 9-8  |

| 9-7  | Air Filtration System .....               | 9-10 |

| 9-8  | PCB Jumper/Terminator Locations .....     | 9-11 |

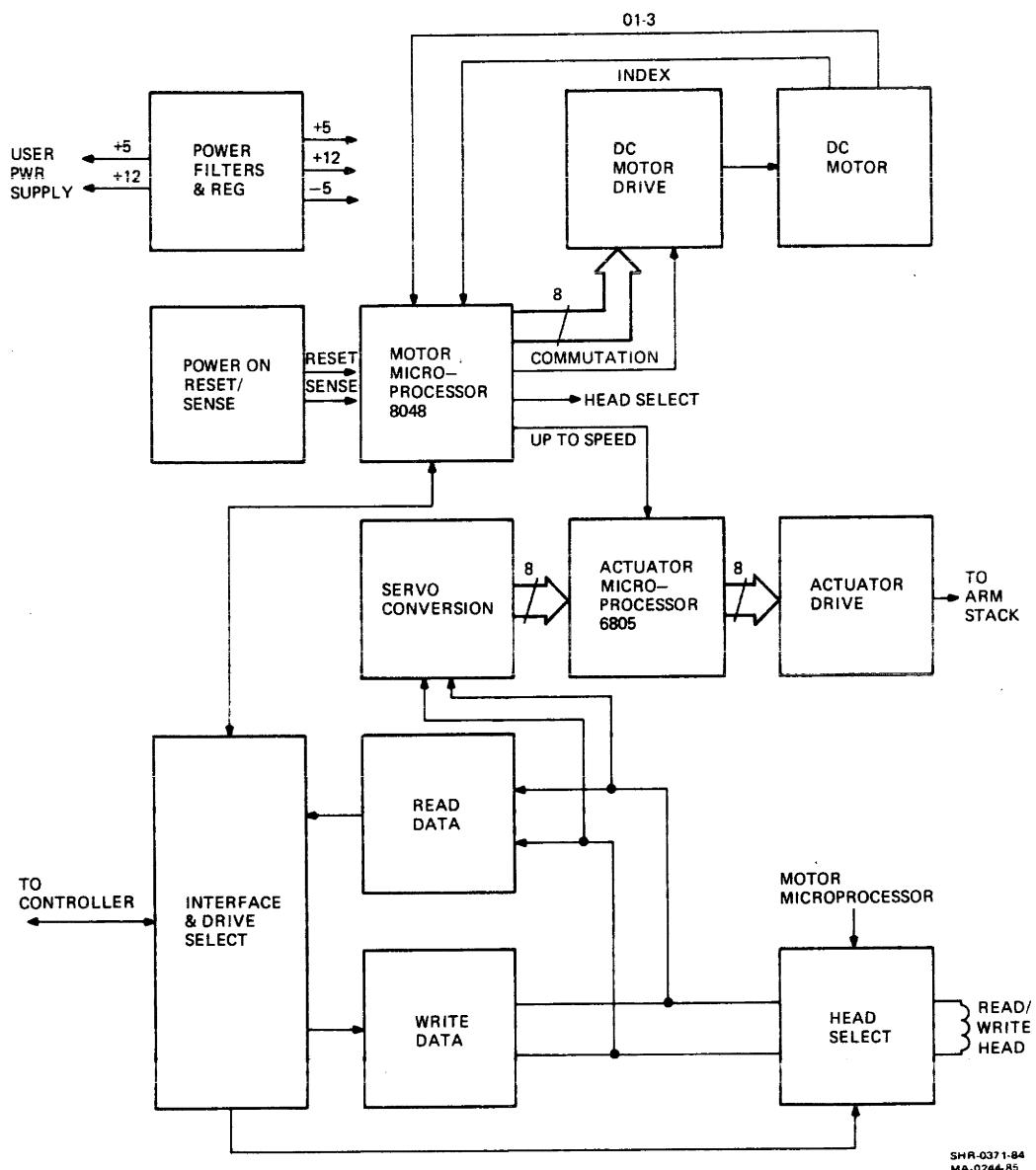

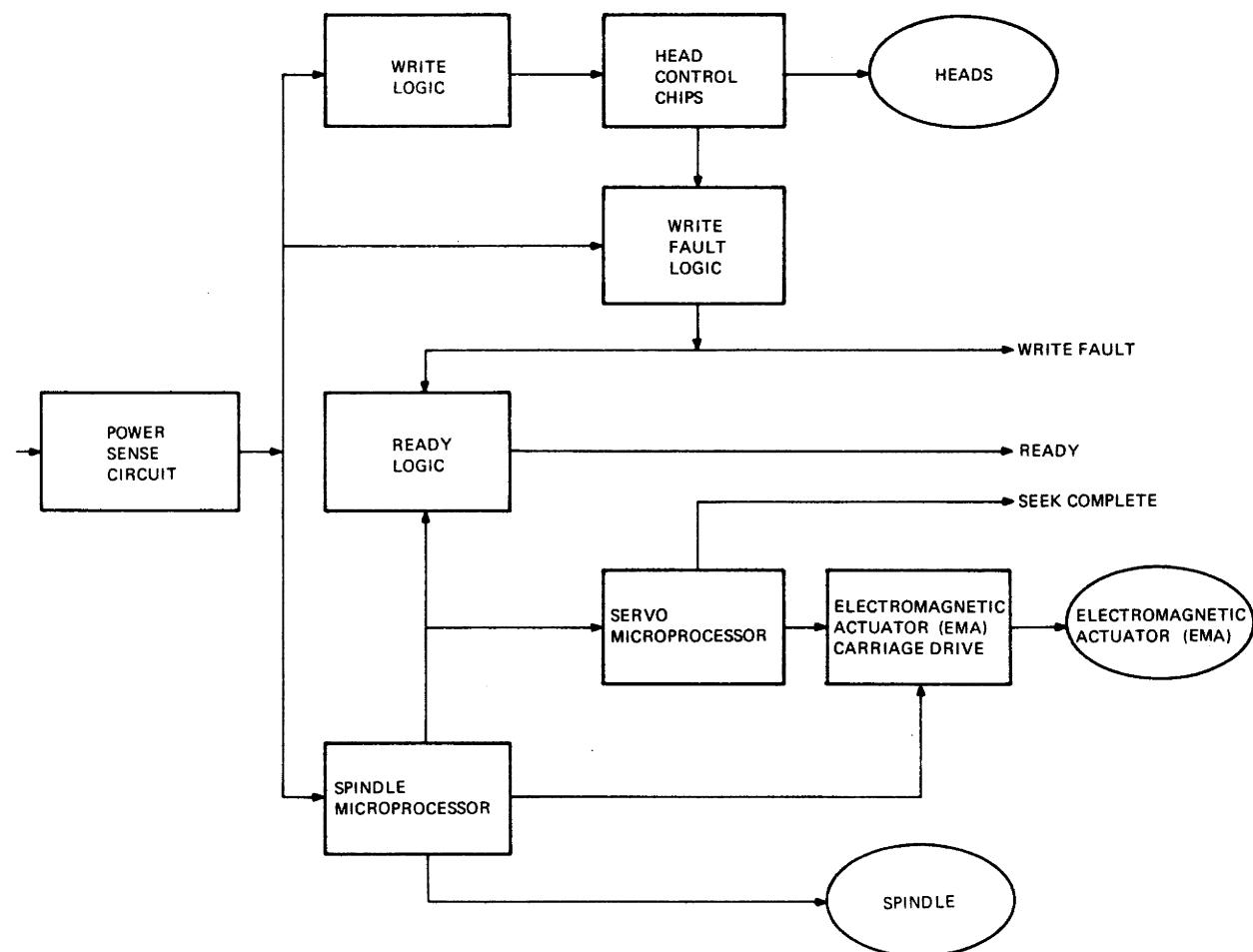

| 9-9  | RD52-A Block Diagram .....                | 9-13 |

| 9-10 | RD52-A Drive Electronics .....            | 9-13 |

| 9-11 | Encoder PCB Block Diagram .....           | 9-14 |

| 9-12 | AGC Circuit .....                         | 9-15 |

| 9-13 | P1 and P2 Generation .....                | 9-15 |

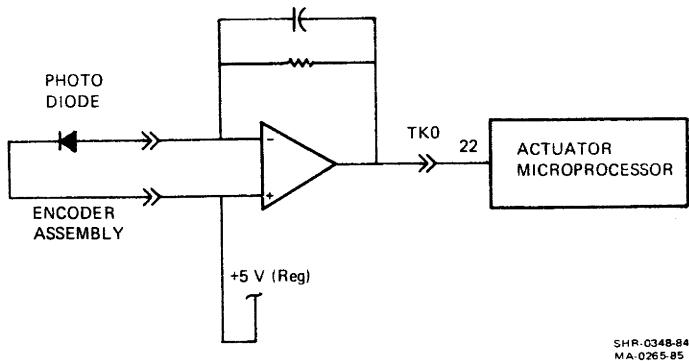

| 9-14 | Track 0 Detector .....                    | 9-16 |

| 9-15 | Control PCB Block Diagram .....           | 9-17 |

| 9-16 | Write Circuit Block Diagram .....         | 9-19 |

| 9-17 | Read Circuit Block Diagram .....          | 9-20 |

| 9-18 | Motor Microprocessor .....                | 9-21 |

| 9-19 | DC Motor Commutation Timing Diagram ..... | 9-22 |

| 9-20 | DC Motor Drive Circuit (Simplified) ..... | 9-24 |

| 9-21 | Wedge and Index Timing .....              | 9-25 |

| 9-22 | Interface Connectors .....                | 9-27 |

| 9-23 | J1 Connector .....                        | 9-27 |

| 9-24 | J2 Connector .....                        | 9-27 |

| 9-25 | Control Signal Driver/Receiver .....      | 9-28 |

| 9-26 | Single Step Mode Timing .....             | 9-29 |

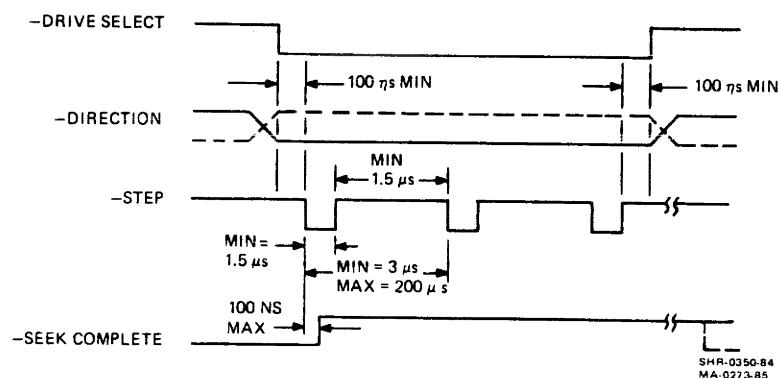

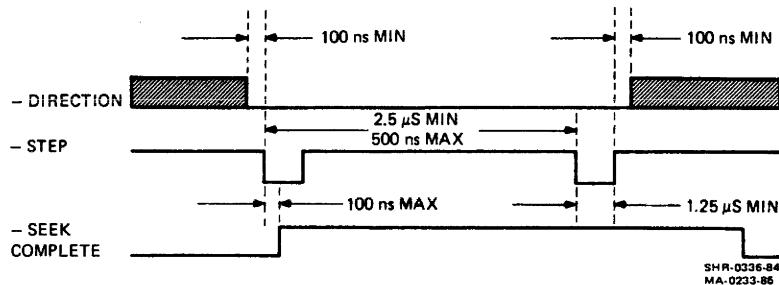

| 9-27 | Buffered Step Mode Timing .....           | 9-29 |

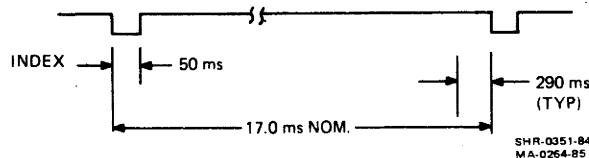

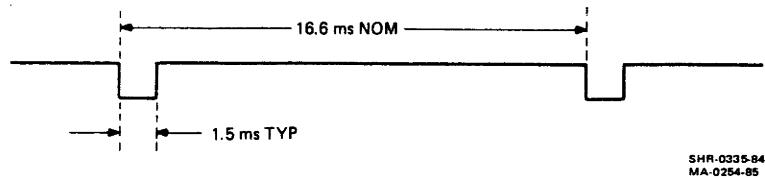

| 9-28 | Index Timing .....                        | 9-30 |

| 9-29 | General Control Timing .....              | 9-31 |

| 9-30 | Data Signal Driver/Receiver .....         | 9-31 |

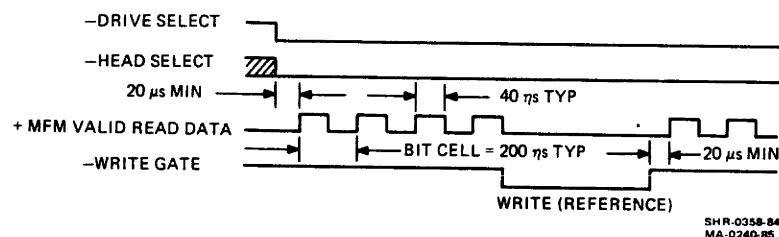

| 9-31 | MFM Write Data Timing .....               | 9-33 |

| 9-32 | MFM Read Data Timing .....                | 9-33 |

| 9-33 | The RD52-A Disk Drive (30-23227-02) ..... | 9-33 |

| 9-34 | Current Requirements .....                | 9-35 |

| 9-35 | +12 V Startup Current .....               | 9-35 |

| 9-36 | J3 Connector Layout .....                 | 9-35 |

| 9-37 | RD52-A Motor Assemblies .....             | 9-37 |

| 9-38 | Jumper/Terminator Locations .....         | 9-38 |

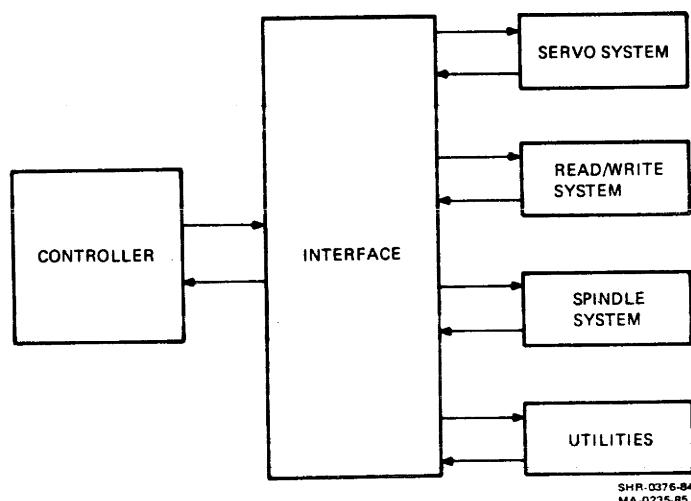

| 9-39 | RD52-A Block Diagram .....                | 9-39 |

| 9-40 | Power Faults .....                        | 9-42 |

| 9-41 | Interface Logic .....                     | 9-43 |

| 9-42 | Read/Write Operations .....               | 9-48 |

| 9-43 | Interface Connector Locations .....       | 9-50 |

| 9-44 | J1 Connector .....                        | 9-51 |

| 9-45 | J2 Connector .....                        | 9-51 |

| 9-46 | Control Signal Driver/Receiver .....      | 9-52 |

| 9-47 | Single Step Mode Timing .....             | 9-53 |

| 9-48 | Buffered Step Mode Timing .....           | 9-53 |

| 9-49 | Index Timing .....                        | 9-54 |

| 9-50 | Data Line Driver/Receiver .....           | 9-55 |

| 9-51 | Read/Write Data Timing .....              | 9-55 |

## TABLES

|      |                                                                                                                          |      |